「ムーアの法則」は終わらない 〜そこに“人間の欲望”がある限り:湯之上隆のナノフォーカス(41)(2/6 ページ)

EUVについての予測調査

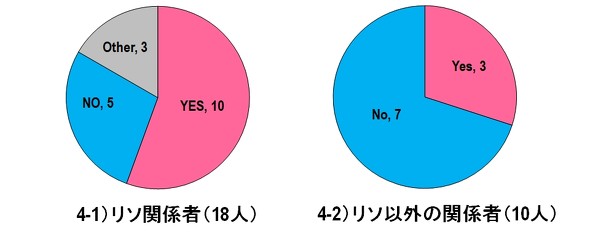

「微細化の限界はhp何nmか」の調査からはちょっと脇道にそれるが、2007年当時、開発が困難を極めていたEUVについて、筆者はA〜Zの関係者たちに、「EUVの量産機はできないのではないか?」という質問をした。その結果を図4に示す。

ここで、例えば半導体メーカーのリソグラフィ技術者やリソに関係する製造装置や材料メーカーの技術者と、リソ以外の技術者、例えば半導体メーカーのインテグレーション技術者やリソ以外の製造装置や材料関係者に分けて図4を作成した。

すると、リソ関係者の18人のうち、過半を超える10人が「Yes(つまりEUV量産機はできない)」と回答している(図4-1)。その反面、リソ以外の関係者10人のうち7人が「No(つまりEUV量産機はできる)」と回答しているのである(図4-2)。この対比が実に面白い。

リソ関係者は、EUV開発の困難さを、いやというほど知っているために「量産機なんかできっこない」と思ってしまうのだろう。ところが、リソ以外の関係者は、「リソ屋はいつも、できない、できないと騒いでいる」と端(はな)からリソ屋を信用していないのである。

そして結果から言うと、2019年にTSMCが7nm+の孔にEUVを量産適用し、2020年には配線にもEUVを適用する5nmが立ち上がった。従って、リソ屋の言うことは正しくないことが証明された。つまり、リソ屋が「できない」ということは信じない方が良いということだ。

今後の微細化の見通し

このように、半導体業界では、歴史的に微細化の限界説は常に打破されて来ており、微細化のペースはスローダウンしているものの止まってはいない。では、今後の見通しはどうなのだろうか?

微細化については、2001年に国際半導体技術ロードマップ(International Technology Roadmap for Semiconductors、ITRS)が決められ、それに沿って微細化が進められるようになった。このロードマップに従って最先端を走っていたのがPC用プロセッサを量産していた米Intelだったために、陰では“Intel Technology Roadmap for Semiconductors”(Intelのためのロードマップ)と言われたりした。

ところが、2016年にIntelが10nmの立ち上げに失敗したときと同じくしてITRSは終わり、その後はInternational Roadmap for Devices and Systems(IRDS)に引き継がれていくが、もう誰も「Intelのロードマップ」とは言わなくなった。

そして、Intelに代わって微細化の最先端に躍り出たのがTSMCであり、半導体のロードマップはIRDSより、欧州のコンソーシアムimecが発表するものの方が現実に近いような気がしている。

そのように筆者は、半導体の微細化を観察しているが、2020年12月にオンデマンドで開催された半導体の国際学会IEEE International Electron Devices Meeting(IEDM)2020におけるimecのSri Samavedam氏によるプレナリートークが素晴らしく良くまとまっていたので、そのスライドを基に2030年までの微細化を展望してみたい。

ロジックCMOSの進化と微細化

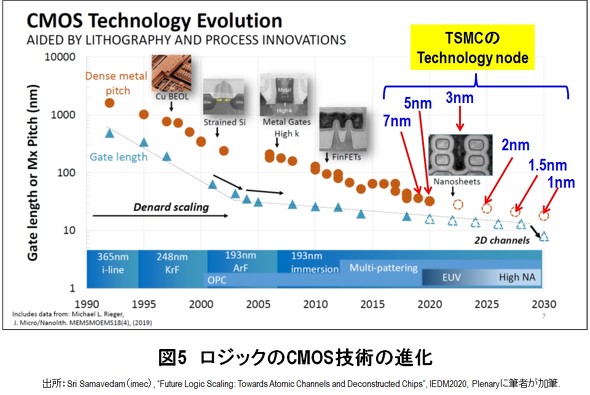

1990年から2030年までのCMOSの進化と微細化の実績および予測を図5に示す。この図1枚で、微細化の過去、現在、未来が一望できる。筆者にとっては感動的な図であった。

図5:ロジックのCMOS技術の進化 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenaryに筆者が加筆(クリックで拡大)

図5:ロジックのCMOS技術の進化 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenaryに筆者が加筆(クリックで拡大)2000年代中旬までは、IBMのRobert H. Dennard氏が提唱したスケーリング則による微細化が順調に進んでいった。つまり、2年で70%の微細化を行い、トランジスタの動作速度、消費電力、集積度を向上させることができていた。

しかし、2003年頃からゲート長の微細化がスローダウンした。この辺りから、微細化しても、トランジスタの動作速度は向上しなくなってしまった。そのため、ブースター技術として、Cu/Low-k配線、歪みSi(Strain Si)、High-k/Metalゲート、FinFETsなどを導入することになった。

また、図5の中で“Dense Metal Pichi”と書かれている最も微細な配線(M1)のスケーリングは、時々スローダウンしながらも続いてきている。

そして、2016年にIntelが10nmの立ち上げに失敗して以降、微細化をけん引する主役はTSMCに移行した。この図に、2018年以降にTSMCが量産した、または今後量産すると予測されるテクノロジーノードを書き込んでみた。

imecのロードマップとTSMCの量産を比べてみると、EUVの適用時期は一致しているが、CMOSにGate All Around(GAA)構造のNanosheetsを使う時期が異なる。imecは3nmを想定しているが、現在リスク生産に入ったTSMCはFinFETであり、Nanosheetsを採用するのは2nmからだと思われる。

いずれにしても、2030年まで、ゲート長も微細配線M1も、スケーリングが止まることは無い。この図によれば、今後10年間は、スローダウンすらしない。むしろ、1nmで2D channelsと呼ばれる新しいCMOS構造が採用された場合、ゲート長の微細化は一気に進むことになっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待