「ムーアの法則」は終わらない 〜そこに“人間の欲望”がある限り:湯之上隆のナノフォーカス(41)(3/6 ページ)

トランジスタと微細配線のスケーリング

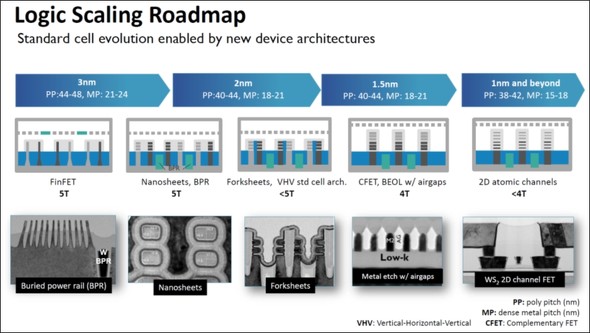

図6に、ロジックのスケーリングに伴うトランジスタ構造の変遷を示す。3nmから2nmにかけて、FinFETからNanosheetsに変化する。また、2nmから1.5nmにかけて、nMOSとpMOSを壁で分けるForksheetsが有望とimecは考えている。これに対して、TSMCの量産計画では、2nmでNanosheetsが使われる模様であるが、Forksheetsが採用されるという話は聞こえてこない。

図6:ロジックのスケーリングのロードマップ(トランジスタ) 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenary(クリックで拡大)

図6:ロジックのスケーリングのロードマップ(トランジスタ) 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenary(クリックで拡大)さらにimecは、1.5nm付近でnMOSとpMOSを縦方向に形成するComplementary FET(CFET)を使うことを想定しているが、これもTSMCのR&Dでは出てきた気配がない。しかし、1nmおよびその先で登場が予想される2D atomic channelsについては、TSMCも同様のR&Dを行っている。

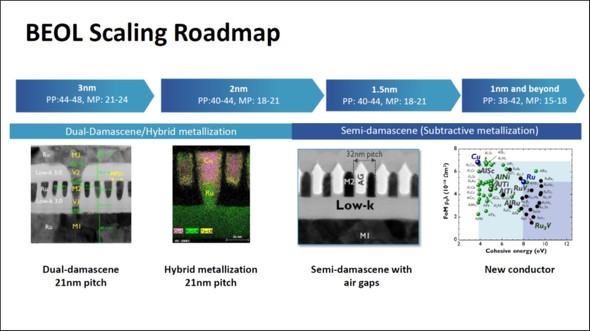

このようにトランジスタにはさまざまな選択肢があり、本当に進化して行きそうであるが、微細配線の開発はかなり深刻である。現在主流となっているCu配線では、配線幅が微細化されると、Cuのグレインによる散乱およびバリアメタルによる散乱による抵抗増大が大問題となる(図7)。

図7:微細配線のスケーリングのロードマップ 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenary(クリックで拡大)

図7:微細配線のスケーリングのロードマップ 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenary(クリックで拡大)現状のCu Dual Damasceneが使えるのは3nmが限界で、2nmからはビアにRuを使うHybridとなり、1.5nmではRuなどを直接加工(Subtractive)した上で、層間絶縁膜をAir Gapにする必要がある。さらに、1nmおよびその先では、まったく新しい材料を探索しなければならないことが示されている。

このように2030年までを見通すと、トランジスタ構造はさまざまな候補があり、最適なものが量産に使われると考えられるが、配線の微細化に伴う抵抗増大の問題は避けがたく、これに対しては材料変更を行うなど、かなり大胆なR&Dが必要になるということである。

EUVのスケーリングのロードマップ

これまで見てきたように、現在から2030年までの間、トランジスタは構造を変えながら、微細配線は形成方法や材料を変更しながら、スケーリングは続く。そのために必要なEUVはどのように変化していくだろうか?

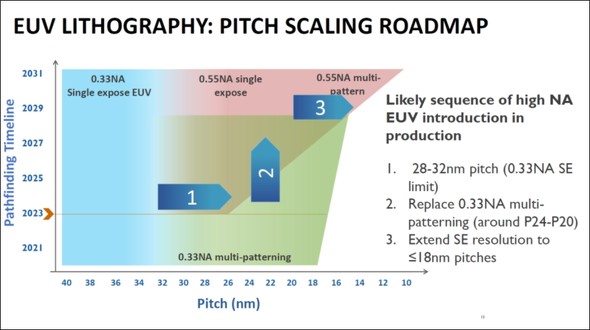

図8は、EUVのスケーリングのロードマップを示している。現在の最先端の微細化では、レンズの開口数NA=0.33のEUV(以下、Regular NAと呼ぶ)が使われている。その後、もっと微細化するためには、次の4段階のロードマップで、EUVのスケーリングが行われる(図8の番号とは少しずれる)。

図8:EUVリソグラフィのスケーリングのロードマップ 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenary(クリックで拡大)

図8:EUVリソグラフィのスケーリングのロードマップ 出典:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020, Plenary(クリックで拡大)- 28〜32nmピッチの微細加工が、Regular NAのEUVのシングル露光の限界となる。

- 22〜24nmピッチでは、Regular NAのEUVでSADPを行う

- 18nmピッチ以降では、NA=0.55(High NAと呼ぶ)のEUVを使う

- さらなる微細加工には、High NA+SADPを使う

このように、2030年までEUVを使ったスケーリングのロードマップが示された。問題は、Regular NAのEUVが160〜180億円であるのに対して、2024年頃に登場するといわれているHigh NAのEUVが(うわさでは)480億円もするということである。果たして、これほど高額な露光装置を使って製造したロジック半導体がビジネスとして成立するのだろうか?

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待