高融点金属の多層配線技術が2nm以降のCMOSを実現:福田昭のデバイス通信(319) imecが語る3nm以降のCMOS技術(22)

前回から「次世代の多層配線(BEOL)技術」の講演内容を紹介している。今回は、銅(Cu)以外の配線技術を導入する際の候補となる高融点金属について解説する。

21nmピッチが銅配線の限界点と予測

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から、「次世代の多層配線(BEOL)技術」の講演パートを紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から、「次世代の多層配線(BEOL)技術」の講演パートを紹介している(クリックで拡大)前回から、5番目のパートである「次世代の多層配線(BEOL)技術」の講演内容を紹介している。主題は、3nm以降の技術世代(技術ノード)を担う多層配線技術である。

前回で述べたように、3nm以降のCMOSロジックでは銅(Cu)のデュアルダマシン技術による多層配線が限界に近づく。imecは限界となる配線ピッチを21nmと予測しており、21nm以降は銅(Cu)以外の配線技術を導入しなければならない。このように考える。

配線層間のビアを高融点金属で埋める

多層配線の導体部分は、平行な直線配線群の層(配線層)と層間を結ぶビア電極で構成される。始めに微細化の限界が来るのは、ビア電極である。そこでビア電極を銅(Cu)ではなく、高融点金属のタングステン(W)やモリブデン(Mo)、コバルト(Co)、ルテニウム(Ru)などに変更する。

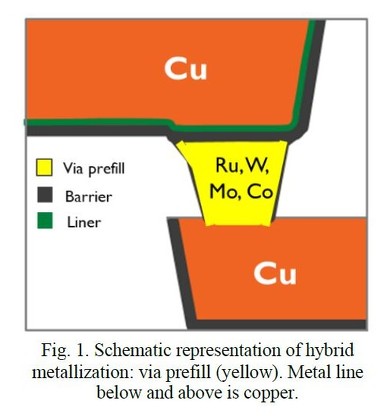

配線層を銅(Cu)、ビア電極を高融点金属で形成する多層配線の断面構造図。出典:imec(IEDM 2020の発表論文「Inflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottleneck」(論文番号32.2)) (クリックで拡大)

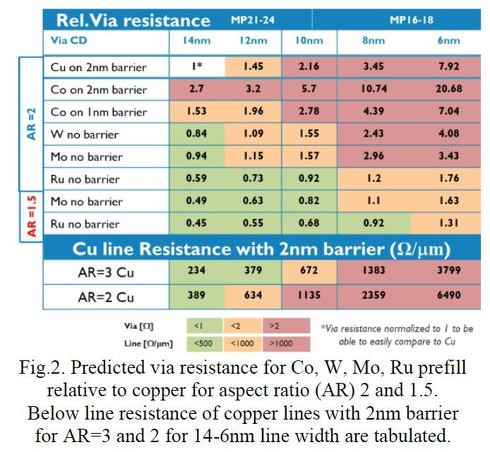

配線層を銅(Cu)、ビア電極を高融点金属で形成する多層配線の断面構造図。出典:imec(IEDM 2020の発表論文「Inflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottleneck」(論文番号32.2)) (クリックで拡大) ビア電極の微細化による抵抗値の変化を銅と高融点金属で比較(計算値)。大きさ14nmのビアをアスペクト比(AR)2の銅(Cu)(バリア層の厚みは2nm)で埋めたときの抵抗値を基準(1)とした相対値である。出典:imec(IEDM 2020の発表論文「Inflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottleneck」(論文番号32.2)) (クリックで拡大)

ビア電極の微細化による抵抗値の変化を銅と高融点金属で比較(計算値)。大きさ14nmのビアをアスペクト比(AR)2の銅(Cu)(バリア層の厚みは2nm)で埋めたときの抵抗値を基準(1)とした相対値である。出典:imec(IEDM 2020の発表論文「Inflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottleneck」(論文番号32.2)) (クリックで拡大)大きさが14nmのビア(配線ピッチ21nm〜24nmの多層配線構造に相当)を厚み2nmのバリア層と銅(Cu)で埋めた場合のビア抵抗(アスペクト比(AR)は2)を基準(1.00)とする。ビアの大きさが10nmに細くなると、抵抗値(相対値)は2.16と基準の2倍を超える。

一方で基準と同じ14nmのビア(ARは2)でバリア層のないタングステン(W)は0.84、バリア層のないモリブデン(Mo)は0.94、バリア層のないルテニウム(Ru)は0.59にビア抵抗(相対値)が下がる。

また銅(Cu)配線の抵抗値(単位長当たり)は、配線幅が14nmでアスペクト比(AR)が3のときに234Ω/μm、ARが2のときに389Ω/μmとなる。配線幅を10nmに細くすると、ARが3のときに672Ω/μm、ARが2のときに1135Ω/μmと抵抗値は約2.9倍に増加する。

ルテニウム(Ru)が将来の多層配線では有望

これらの推定から、imecは将来有望な金属をルテニウム(Ru)と考えている。抵抗率が低いことと、バリア層が不要であること、エッチングによって加工できること、などが有望視する理由だ。

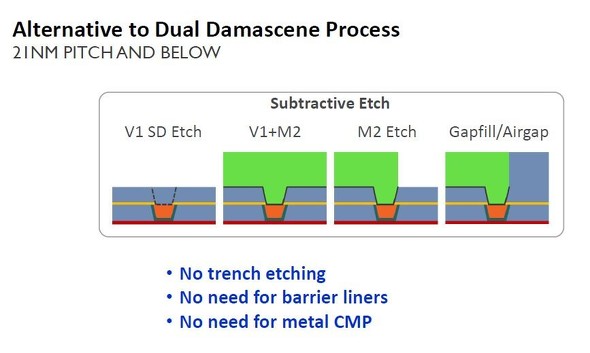

そこで「セミダマシン(Semi-Damascene)」と呼ぶ技術によってルテニウム(Ru)の多層配線構造を開発中である。セミダマシン技術では、下層の配線層の上に絶縁層を成膜し、ビアをエッチングで形成する。それから上層の配線層(Ru層)とビアをまとめて成膜する。それからビアの周囲をエッチングし、絶縁膜で埋めるか、あるいはエアギャップとして残す。

セミダマシン(Semi-Damascene)の配線形成プロセス。成膜とエッチングによって配線とビア電極を形成する。ビアの周囲は絶縁膜あるいはエアギャップとなる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

セミダマシン(Semi-Damascene)の配線形成プロセス。成膜とエッチングによって配線とビア電極を形成する。ビアの周囲は絶縁膜あるいはエアギャップとなる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス エレクトロニクスは2021年7月29日、2021年12月期第2四半期(4〜6月)業績(Non-GAAPベース)を発表した。第2四半期3カ月間の売上高は2179億円で前年同期比30.7%増、営業利益は614億円で同2.03倍と大幅な増収増益になった。売上総利益率は52.0%、営業利益率は28.2%だった。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待