Samsung、2022年前半にGAA適用の3nmチップの生産開始:生産能力も2026年までに3.2倍へ

Samsung Electronicsファウンドリー部門は、2021年10月6〜8日にオンラインで開催した「Samsung Foundry Forum 2021」で、半導体プロセスのロードマップと製造工場の拡張について詳細を明らかにした。Samsungは、次世代のトランジスタ技術の開発を最も積極的に進めており、TSMCやIntelに先駆けて量産を開始する計画だ。

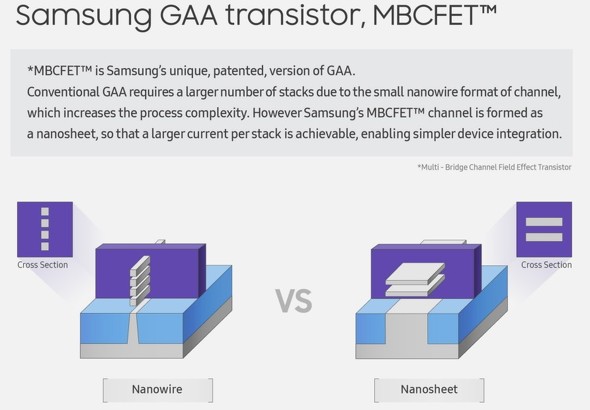

Samsung Electronics(以下、Samsung)のファウンドリー部門は、2021年10月6〜8日にオンラインで開催した「Samsung Foundry Forum 2021」で、半導体プロセスのロードマップと製造工場の拡張について詳細を明らかにした。Samsungは、次世代のトランジスタ技術の開発を積極的に進めており、TSMCやIntelに先駆けて量産を開始する計画だ。Samsungは、同社が「MBCFET(Multi Bridge Channel FET)」と呼ぶGAA(Gate-All-Around)トランジスタ構造を適用して、2022年前半に3nmプロセスの生産を開始するという。一方のTSMCは、同社が「N2」と呼ぶ2nmプロセスの2023年の完成を待って、GAAを適用するとしている。

Intelは2024年半ばに、「RibbonFET」と呼ぶGAAトランジスタを適用して、「20A(2nm)」プロセスの生産を開始する。Samsungがこの技術の開発を最も積極的に進めているのに対し、TSMCはFinFET設計の適用を延ばすという、より保守的なアプローチで、2022年前半に3nmノードを実現するとしている。また、Intelは、2022年に「Intel 4」ノードに、2023年に「Intel 3」ノードに、それぞれ「Enhanced SuperFin」トランジスタを適用する。これらの新しいノードは全て、FinFETとGAAの両方ともEUV(極端紫外線)リソグラフィを使用している。なお、SamsungとTSMCは少なくとも現時点では、Intelのようにノード名をナノメートルからオングストロームに変更するとは決定していない。

Samsungが開発したGAA(Gate-All-Around)トランジスタ。設計者はデバイスのチャンネル幅を調整することで、電力と性能のバランスを取ることができるという 出所:Samsung Foundry

Samsungが開発したGAA(Gate-All-Around)トランジスタ。設計者はデバイスのチャンネル幅を調整することで、電力と性能のバランスを取ることができるという 出所:Samsung FoundryGAAの初期バージョンは2022年末に量産開始

Samsungの最初のGAAノードはGAAの初期バージョンである「3GAE(3nm Gate-All-Around Early)」で、2022年末に量産を開始する。その後2023年末に、GAAの改良版である「3GAP(3nm Gate-All-Around Plus)」ノードの量産を開始する。2GAPノードの量産は2025年以降になる見通しだ。Samsungの幹部はフォーラムの前に行われた記者会見で、「新しいMBCFET技術は製造コストが高いが、トランジスタ当たりのコストを下げるために努力する」と述べている。3nm MBCFETノードは、5nmプロセスと比較して面積を最大35%削減、性能を30%高め、消費電力を50%削減できるという。

なお、最先端のGAAプロセスの開発に深く関わっているのがIBMだ。IBMは製造工場自体は持っていないが、米国ニューヨーク州アルバニーのAlbany NanoTech Complexにある研究所を拠点として、GAAプロセスの研究開発を行っている。Samsungは同プログラムに参加しており、2021年にはIntelも参加している。SamsungのイベントにはIBMとIntelの両社が登場したが、それはこうした理由からかもしれない。Samsungは、IBMの最新プロセッサである「Power 10」および「Telum」のファウンドリーパートナーでもある。

では、なぜGAAはこれほどまでに重要なのだろうか。それは、GAAを適用すると、ゲートをより正確にコントロールできるからだ。FinFETではフィンの数がばらばらで、高さのコントロールが限られていたのに対し、GAAはナノシートの幅やスタッキングをよりコントロールすることができる。それにより、ゲートの静電的な制御が向上し、ひいてはゲートの小型化につながる。

そうした制御の向上によって、供給電圧を下げることができ、トランジスタの電力も削減できる。GAAの初期のプロトタイプにはナノワイヤが用いられていたが、量産される全てのGAAトランジスタでは、幅を変えられるナノシートを用いる。これにより、トランジスタのサイズや駆動能力をFinFETに比べさらにきめ細かくコントロールすることができる。

RFなど向けに17nm FinFETも

なお、Samsungは引き続き、RFなどの専門的なアプリケーションに向けて14nmならびに17nmのFinFETを開発していく方針だ。同社はこれまでも、14nmのフロントエンドプロセスと、28nmのバックエンドプロセスを組み合わせた17nmノードを開発することで、28nmのプレーナ型トランジスタとのギャップを埋めてきた。また、同社の5nmノードは車載向けにも適用する予定だ。

チップレット、タイル、2.5D(次元)/3Dなど選択肢が増えるにつれ、新たなパッケージング技術は全てのファウンドリーにとって必要不可欠なものとなってきた。Samsungはこれらのパッケージングの選択肢について、異種統合に向けた『ムーアを超えるもの』と呼んでいる。同社はIntelやTSMCに遅れないよう、3D IC、マイクロバンプ、ハイブリッドボンディング、3.5Dの選択肢を提供する予定だという。TSMCには、CoWoS(Chip on Wafer on Substrate)、InFO(Integrated Fan-Out)、SoIC(System on Integrated Chips)といった自社技術で培った、パッケージングの強力なロードマップと実績がある。パッケージングを近年の技術サミットでの主要なトピックにしたのもTSMCだ。IntelのFoverosやEMIBも同様に差別化要因とうたわれている。

生産能力も2026年までに3.2倍に

Samsungは他にも重要な発表をした。同社は、米国に建設する新たな製造施設を含め、2026年までに生産能力を3.2倍に拡大する計画だという。同社はこの施設の場所や規模、スケジュールについては明らかにしていないが、テキサス州オースティンには既に製造施設(S2)がある。また、Samsungは、最近の半導体不足の大部分を占めるレガシーノードの製造施設の拡大も検討している。一方、TSMCはアリゾナ州フェニックスに5nmプロセスを適用する工場を建設する。またIntelのアリゾナ州チャンドラーのキャンパス内では、新たに2つの工場の建設が始まった。

SamsungとTSMC間のファウンドリー競争は緩やかになる兆しがなく、今やそこにIntelが加わりつつある。Samsungは3nmプロセスの生産を初めて実現する企業にはならないかもしれないが、同社のGAAトランジスタはより優れた性能と電力特性を備えているはずだ。Samsungにとっての課題は、2024年にTSMCがN2ノード、Intelが20Aノードでの量産をそれぞれ開始した後でも首位を維持することにある。

【翻訳:滝本麻貴、青山麻由子、編集:EE Times Japan】

関連記事

IBMが「2nm」プロセスのナノシートトランジスタを公開

IBMが「2nm」プロセスのナノシートトランジスタを公開

IBMは、米国ニューヨーク州アルバニーにある研究開発施設で製造した「世界初」(同社)となる2nmプロセスを適用したチップを発表した。同チップは、IBMのナノシート技術で構築したGAA(Gate-All-Around)トランジスタを搭載している。 チップレットと3次元集積が「ムーアの法則」を牽引

チップレットと3次元集積が「ムーアの法則」を牽引

今回から、2021年8月にオンラインで開催された「Hot Chips」の技術講座より、「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」の講演内容を紹介する。 市場急拡大の反動、「メモリ大不況」はいつやってくる?

市場急拡大の反動、「メモリ大不況」はいつやってくる?

続々と巨額の投資が発表される半導体業界。現状は半導体不足が続いているが、どこかで供給が需要を追い越し、そのあとには半導体価格の大暴落と、それに続く半導体の大不況が待ち構えているとしか考えられない 「PIMの可能性を広げる」、Samsung

「PIMの可能性を広げる」、Samsung

Samsung Electronics(以下、Samsung)は、PIM(Processing-in-Memory)を主流派の技術へと推進していく上で、新たなステップの実現を発表した。同社は2021年初めに、PIM技術を他の種類のメモリに統合するという構想の一環として、業界で初めて、PIM対応のHBM(High Bandwidth Memory)である「HBM-PIM」を、商用化されたアクセラレーターシステムに統合することに成功している。 Samsung、米国新工場建設で3つの州と交渉

Samsung、米国新工場建設で3つの州と交渉

Samsung Electronicsが、米国内に170億米ドル規模の半導体工場を建設すべく、3つの州との間で交渉を進めているという。早ければ2024年末にも製造を開始するとみられる。世界第2位の半導体メーカーである同社は、「米国から十分な助成金を得られない場合は、本社を置いている韓国に新工場を設立する可能性もある」と述べている。 Intelのアリゾナ新工場、建設がスタート

Intelのアリゾナ新工場、建設がスタート

Intelは2021年9月24日(米国時間)、米国アリゾナ州チャンドラーの工場「Ocotillo Campus(オコティージョ・キャンパス)」に、新たに建設する2棟の工場の着工式を開催した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

MBCFET技術の利点 出所:Samsung Foundry

MBCFET技術の利点 出所:Samsung Foundry