SiC-MOSFETの性能が6〜80倍に、トレンチ型に応用可能:界面の欠陥低減と平たん性向上で(3/3 ページ)

» 2021年10月27日 09時30分 公開

[村尾麻悠子,EE Times Japan]

SiC-MOSFETのオン抵抗は半減

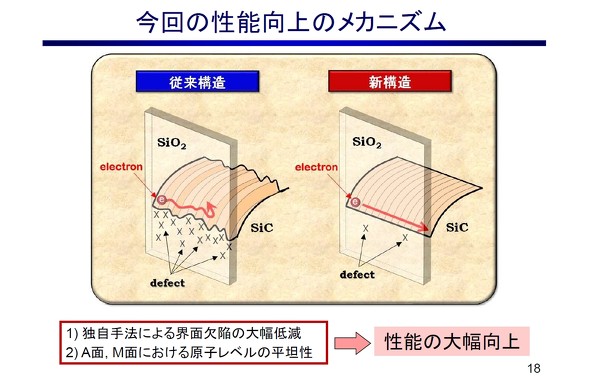

今回の性能向上のメカニズムを、模式的に表したものが下の図だ。独自手法の酸化膜生成に加え、界面が極めて平たんなA面/M面を使うことが、性能向上に貢献した。

なお、今回木本氏らはプレーナ型SiC-MOSFETで評価をしたが、これをトレンチ型に応用して製造する場合でも、「大幅なコスト増にはならないだろう」とみる。特殊な装置や高価な原材料も不要で、「工程が数個増えると思うが、それが致命的なコスト増にはならないと考えている」(同氏)

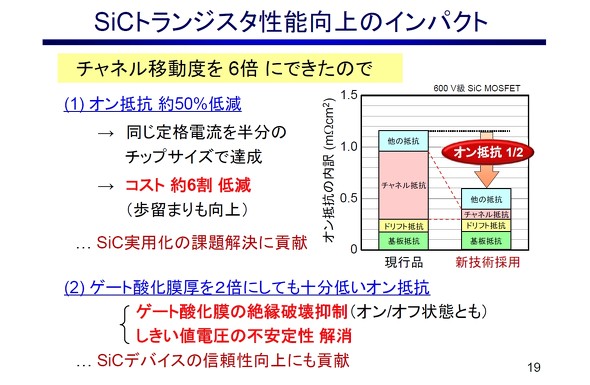

今回、チャネル移動度が6倍(80倍という結果も得られたが、6倍という数字を使う)に向上したので、耐圧600VのSiC-MOSFETでは、チャネル抵抗が既存品の6分の1になる。他の抵抗成分と合わせると、SiC-MOSFET全体でオン抵抗を約半分に削減できるという。同じ定格電流であれば、チップサイズが半分で済むということだ。これによりコストも約6割削減できると木本氏はみている。

SiCウエハーでは大口径化も進められているが、木本氏は8インチSiCウエハーでも今回の効果は有効ではないかとする一方で、ウエハー全面の均一性については課題になるとした。

2020年8月の発表に続き、今回はより実用的なSiC-MOSFETへの適用を見据えた研究結果となった。ただ、木本氏は今回の結果でも「満足はしていない」と述べる。「本来であれば(チャネル移動度は)200や250cm2/Vsといった数字が出るはずなので、これから欠陥の低減などを進め、SiCパワートランジスタのさらなる性能向上を目指す」(木本氏)

関連記事

「数十年に一度のブレークスルー」が当たり前の世界

「数十年に一度のブレークスルー」が当たり前の世界

30年って長いですよね……。人生の3分の1ですもん。 新手法の酸化膜形成でSiC-MOSFETの性能が10倍に

新手法の酸化膜形成でSiC-MOSFETの性能が10倍に

SiCパワー半導体で30年来の課題となっていた欠陥の低減が、大きく前進しようとしている。京都大学と東京工業大学(東工大)は2020年8月20日、SiCパワー半導体における欠陥を従来よりも1桁低減し、約10倍の高性能化に成功したと発表した。 量産間近の酸化ガリウムSBD、評価ボードも入手可能

量産間近の酸化ガリウムSBD、評価ボードも入手可能

京都大学発のベンチャーで、酸化ガリウムパワーデバイスの開発を手掛けるFLOSFIAは、「TECHNO-FRONTIER 2021」(2021年6月23〜25日/東京ビッグサイト 青海展示棟)に出展し、酸化ガリウムを使用したSBD(ショットキーバリアダイオード)「GaO-SBD」を搭載した評価ボードなどを展示した。 パワー半導体、2030年に4兆471億円規模へ

パワー半導体、2030年に4兆471億円規模へ

パワー半導体市場は2020年の2兆8043億円に対し、2030年は4兆471億円規模に達する見通し――。富士経済が、SiC(炭化ケイ素)などの次世代パワー半導体とSi(シリコン)パワー半導体の世界市場を調査した。 インフィニオン、300mmウエハー新工場の操業開始

インフィニオン、300mmウエハー新工場の操業開始

Infineon Technologies(以下、Infineon)は、オーストリアのフィラッハに建設中だった300mmのウエハー対応の新工場の操業を開始。2021年9月17日(ドイツ時間)に開催したオープニング式典や記者会見で、その内容を説明した。 産総研ら、SiCウエハーの高速研磨技術を開発

産総研ら、SiCウエハーの高速研磨技術を開発

産業技術総合研究所(産総研)は、パワー半導体用大口径SiC(炭化ケイ素)ウエハーの高速研磨技術を、ミズホや不二越機械工業と共同開発した。従来に比べ鏡面研磨を12倍の速度で行えるため、加工時間を大幅に短縮することが可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 次世代パワー半導体 「期待の5材料」の現在地――電子版2026年3月号

- ソニー・ホンダモビリティ、EV「AFEELA」開発中止

Special SitePR

あなたにおすすめの記事PR