東芝、次世代パワー半導体向けドライバーICを開発:アナログとデジタル回路を混載

東芝は、次世代パワー半導体向けのゲートドライバーICを開発した。アナログとデジタル回路を1チップに集積しており、パワー半導体で発生するノイズを最大51%も低減することができるという。2025年の実用化を目指す。

パワー半導体で発生するノイズを最大51%も低減

東芝は2021年10月、次世代パワー半導体向けのゲートドライバーICを開発したと発表した。アナログとデジタル回路を1チップに集積しており、パワー半導体で発生するノイズを最大51%も低減することができるという。2025年の実用化を目指す。

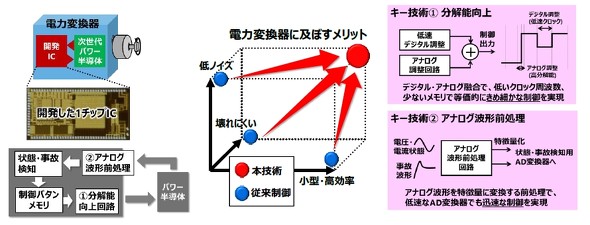

開発したゲートドライバーICは、パワー半導体の電圧や電流をアナログ回路で検知する。その結果に基づき、デジタル回路で制御方法を切り替える。このため、わずかな部品数で適切な制御を可能とした。制御する時は、低速のデジタル回路と高速のアナログ回路を組み合わせた分解能向上回路によって、高速制御を必要とする部分だけアナログとし、きめ細かな制御を実現したという。

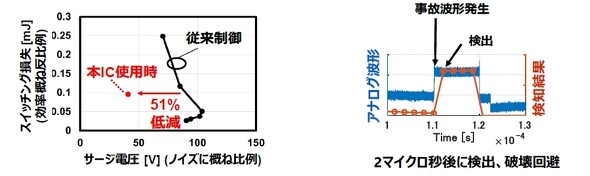

また、パワー半導体の高速な電圧、電流波形から、制御や事故の検知に必要な特徴量だけを抽出するアナログ波形の前処理技術を開発。この技術を用いることで、低速なアナログデジタル変換器で故障を検知することができ、短絡が生じてもパワー半導体を速やかに保護することが可能となった。事故状態を検知する時間は、最短2マイクロ秒だという。CMOSプロセス技術を用いているため、製造コストも安価に抑えることができる見通しだ。

開発したゲートドライバーICを用いると、1.2kVのSiC-MOSFETパワー半導体を制御することができる。しかも、電力損失を増やさず、ノイズ発生の要因となるサージ電圧を約半分に削減した。従来方式で、サージ電圧を同等レベルまで低減すると、モーター駆動時の損失が増えていたという。理論計算によると、開発したゲートドライバーICは、電力損失を25%も低減できることが分かった。

関連記事

次世代リチウムイオン電池の商業化に向け共同開発へ

次世代リチウムイオン電池の商業化に向け共同開発へ

東芝と双日、ブラジルCBMMは2021年9月24日、ニオブチタン系酸化物(以下、NTO)を用いた次世代リチウムイオン電池の電池の商業化に向けた共同開発契約を締結したと発表した。 40V/2.0AステッピングモータードライバーIC発売

40V/2.0AステッピングモータードライバーIC発売

東芝デバイス&ストレージは、電流検出部を内蔵した40V/2.0AステッピングモータードライバーIC「TB67S539FTG」を開発、販売を始めた。外付け部品を削減することができ、実装基板の省スペース化が可能になる。 ペロブスカイト太陽電池で変換効率15.1%を実現

ペロブスカイト太陽電池で変換効率15.1%を実現

東芝は、エネルギー変換効率が15.1%という、世界最高レベルのフィルム型ペロブスカイト太陽電池を開発した。「1ステップメニスカス塗布法」と呼ぶ新たな成膜法を開発することで実現した。 TXZ+ファミリ アドバンスクラスにM4Gグループ

TXZ+ファミリ アドバンスクラスにM4Gグループ

東芝デバイス&ストレージは、Arm Cortex-M4搭載32ビットマイコン「TXZ+ファミリ アドバンスクラス」として、新たに「M4Gグループ」20製品の量産を始めた。高速データ処理が求められるオフィス機器やFA機器、IoT(モノのインターネット)家電などの用途に向ける。 ゲノム解析データを安全に分散保管する実験に成功

ゲノム解析データを安全に分散保管する実験に成功

東芝と東北大学東北メディカル・メガバンク機構、東北大学病院および、情報通信研究機構は、量子暗号通信技術と秘密分散技術を組み合わせたデータ分散保管技術を開発、この技術を用いゲノム解析データを複数拠点に分散し安全に保管する実証実験に成功した。 性能と演算量を調整可能なスケーラブルAI技術

性能と演算量を調整可能なスケーラブルAI技術

東芝と理化学研究所(理研)は、学習済みAIの性能をできる限り落とさずに、演算量を調整できる「スケーラブルAI技術」を開発した。プロセッサの処理能力が異なる応用システムの場合でも、AIエンジンの共有化が可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増