半導体製造装置と材料、日本のシェアはなぜ高い? 〜「日本人特有の気質」が生み出す競争力:湯之上隆のナノフォーカス(45)(4/6 ページ)

3D IC時代のパラダイム・シフト

筆者が微細加工の技術者だった1987〜2002年に、後工程やパッケージを意識したことがなかった。また、2003〜2008年に同志社大学の経営学の教員として、後工程を調査しようとしたときに、その関係者から、『「士農工商、後工程」ということを知っているか?』と言われたことを記憶している。

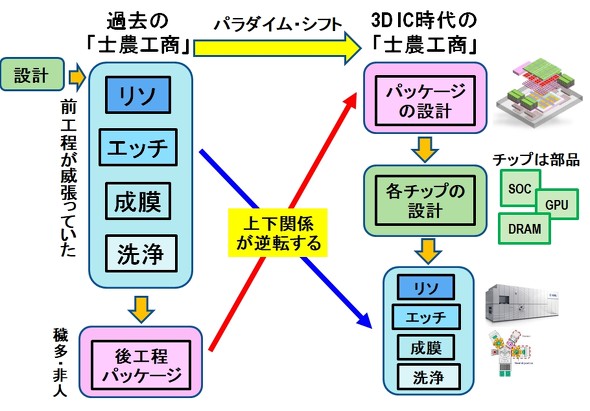

つまり、半導体のプロセスの世界には明確なヒエラルキーがあるのだ(図8)。2010年頃までは、前工程が威張っていた。その中でも、リソグラフィ技術者が最も上位に君臨しており、「リソができなければエッチは何もできないだろう」とか「リソでパターニングしてしまえば後は自動的にトランジスタができる」と言われたことすらある。

そして、後工程/パッケージは、その前工程の「士農工商」にすら入れてもらえず、江戸時代の「穢多・非人」のように、下の下に見られていたということである(筆者もそう見ていた1人である)。

ところが時代は変わった。現代の先端半導体においては、TSMCなどのファンドリー、IntelやSamsung ElectronicsなどのIntegrated Device Manufacturer(IDM)、そしてOutsourced Semiconductor Assembly and Test(OSAT)が競って3D ICを開発している。

その3D ICにおいて、最初に行われるのは、パッケージの設計である。3D ICに組み込まれるSoC(System on Chip)、GPU、DRAMなどのチップは、もはや「部品」である。その「部品」を製造するために、前工程の要素技術が存在する。このように、前工程と後工程/パッケージのヒエラルキーは逆転した。

その結果、俄然、後工程/パッケージが注目される時代に突入したわけだが、この分野の装置や材料の日本シェアはどうなっているだろうか?

後工程プロセスの概要とパッケージが果たしている役割

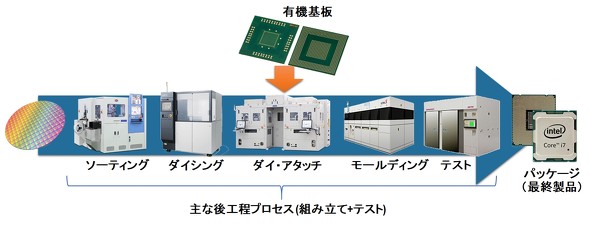

図9に、後工程プロセスの概要を示す。前工程でシリコンウエハ上に1000個程度のチップがつくり込まれ、それが後工程のダイシングによって個片化され、基板材料にアタッチされ、各種テストが行われて、パッケージングされた最終製品が完成する。

ここで前工程と違って後工程が複雑なのは、チップが搭載される(主として有機)基板が、用途や企業によって異なっているということである。つまり、前工程のシリコンウエハのような世界標準の基板が後工程ではないため、それが後工程を理解することを、難しくしている。

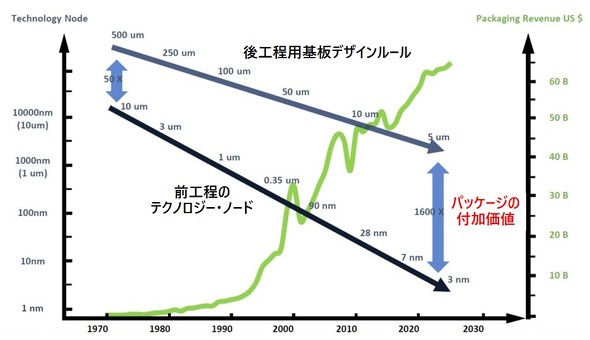

また、後工程のデザインルールは、前工程のテクノロジー・ノードより3桁大きい(図10)。現在でいえば、前工程ではTSMCが5nmの量産を行っているが、後工程に使われる基板のデザインルールは5μmである。

図10:前工程のテクノロジー・ノードと後工程のプロセスルールの差およびパッケージの付加価値[クリックで拡大] 出所:Yole 2020年 、IMAPS Device Packaging Conference

図10:前工程のテクノロジー・ノードと後工程のプロセスルールの差およびパッケージの付加価値[クリックで拡大] 出所:Yole 2020年 、IMAPS Device Packaging Conferenceこれを見て、「微細化しているほどエライ」という思考にどっぷりつかっている前工程の技術者は、「後工程なんてMEMSレベルじゃないか」と見下す人もいるかもしれない。しかし、これは大間違いである。というのは、もし、後工程用基板のデザインルールが、前工程の微細化に追随してしまったら、パッケージされた最終製品がとんでもなく高価になってしまうからだ。

いうなれば、パッケージは、あえて前工程の微細化を追随しないことにより、最終製品の価格を抑えることに多大な貢献をしているのである。ここに、パッケージの最大の付加価値がある。微細化が進めばいいというものではないのである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増