「CXL」ベースのアクセラレータープラットフォーム:メモリ容量を最大2Tバイト増加

オープンな業界標準インターコネクト規格「Compute Express Link(CXL)」のエコシステムには、多くのベンダーが参加している。アクセラレーターも同エコシステムの一部で、米国のファブレス半導体メーカーであるAstera Labs(以下、Astera)が最近発表したCXL 1.1/2.0向けメモリアクセラレータープラットフォーム「Leo」も含まれる。

オープンな業界標準インターコネクト規格「Compute Express Link(CXL)」のエコシステムには、多くのベンダーが参加している。アクセラレーターも同エコシステムの一部で、米国のファブレス半導体メーカーであるAstera Labs(以下、Astera)が最近発表したCXL 1.1/2.0向けメモリアクセラレータープラットフォーム「Leo」も含まれる。

Astera Labs共同設立者でCBO(最高事業責任者)を務めるSanjay Gajendra氏はインタビューの中で、「Leoは、プロセッサのメモリ帯域のボトルネックと容量の制限に対処するために設計した」と述べている。Leo CXLメモリアクセラレータープラットフォームを使用すると、CPUがCXLに接続されたDRAMと永続メモリにアクセスして、これらのメモリを管理できるようになるため、集約型のメモリリソースをより効率的に利用して、性能を低下させずにアクセスをスケールアップすることができる。

Gajendra氏によると、AsteraのLeoプラットフォームは、超低レイテンシを維持しながら、メモリ全体の帯域幅を1レーン当たり32GT/秒に高め、容量を最大2Tバイト増加させるという。クラウドでの運用を確実に拡張する機能の他、大規模なエンタープライズサーバやクラウドサーバの展開に必要な管理および診断機能も備えている。Gajendra氏は、「昨今は、大量のデータを処理するデータセンターで帯域幅を拡張する必要性についての議論が活発だが、それと同様に複雑さも急速に高まっている。複雑さは3カ月半ごとに2倍になっている」と指摘している。

クラウドで機械学習などのAI(人工知能)技術が主流になってきていることで、複雑さが増しているが、これはAsteraの大きな存在意義でもある。

同社は、AIを含む特定のワークロード向けに設計されたアクセラレーターやその他のチップの接続方法など、インターコネクト関連の課題を解決するために、2018年4月に設立された。Gajendra氏は、「接続に必要な方法が従来とは大きく異なることが、CXL技術の開発に向けたIntelとの協業につながった」と述べている。同社は最近、カナダのトロントに設計センターを開設した。

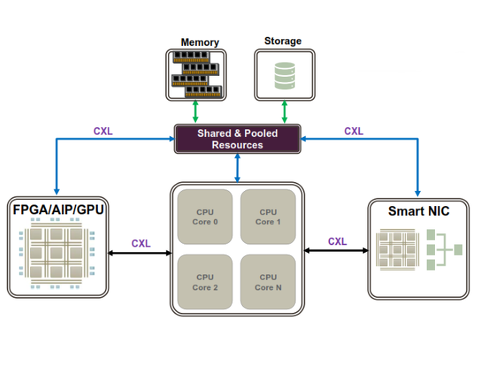

クラウドでのAIの実現には、汎用プロセッサや固有のワークロードに対応できるプロセッサなど、複数の種類のプロセッサが存在するコンピュータアーキテクチャが必要である。これらのプロセッサは多くのデータを生成および消費するため、キャッシュコヒーレンシが特に重要になる。Asteraは2020年に、帯域幅を倍増しサーバでの遅延を低減するCXLリタイマー技術「Aries」を発表したが、Gajendra氏によると、現在はサーバトゥスイッチ(server to switch)およびスイッチトゥスイッチ(switch-to-switch)の帯域幅ボトルネックの対応に取り組んでいるという。同社は、これらの課題を新しい「Taurus Smart Cable Module(Taurus SCM)」で解決するとしている。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

Samsung、CXL関連ポートフォリオにソフトウェアを追加

Samsung、CXL関連ポートフォリオにソフトウェアを追加

Samsung Electronics(以下、Samsung)は、同社初のCXL(Compute Express Link)製品を強化するため、同プロトコルの採用促進やエコシステムの拡張を促すよう開発されたソフトウェアツールを、CXL製品ポートフォリオに追加した。 堅調に成長するCXLエコシステム

堅調に成長するCXLエコシステム

Micron Technologyが3D XPointの開発から撤退したことが話題となった。急速に台頭するインターコネクト規格「Compute Express Link(CXL)」に注力することを選んだためだという。だがもちろん、CXL関連製品を発表したのは、同社が初めてではない。 Micronが「3D XPoint」開発から撤退へ、工場も売却

Micronが「3D XPoint」開発から撤退へ、工場も売却

Micron Technology(以下、Micron)は2021年3月16日(米国時間)、同社がIntelと共同開発した不揮発メモリ「3D XPoint」の開発から撤退し、CXL(Compute Express Link)を用いる新しいメモリ製品への開発へとリソースを移行すると発表した。 キオクシアの四半期業績、売上高が過去最高を記録

キオクシアの四半期業績、売上高が過去最高を記録

今回は、キオクシアの2021会計年度第2四半期(2021年7月〜9月期)の業績を紹介する。 東芝が3社に分割へ、デバイスとインフラサービスを分離

東芝が3社に分割へ、デバイスとインフラサービスを分離

東芝は2021年11月12日、東芝本体からデバイスとインフラサービスの両事業をそれぞれ分離し、計3つの独立会社に分割する方針を発表した。東芝本体は東芝テックとキオクシアホールディングスの株式を管理する会社となるが、キオクシアの株式については、約40%保有する全株を売却する予定だ。同社は2023年度下期までに2つの新会社の独立および上場完了を目標としている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長