3次元集積化技術「SoIC」の開発ロードマップ:福田昭のデバイス通信(339) TSMCが開発してきた最先端パッケージング技術(12)(1/2 ページ)

今回は、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」の開発ロードマップを紹介する。

5nm世代のシリコンダイを使うSoICは2022年に生産を開始

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」がことし(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

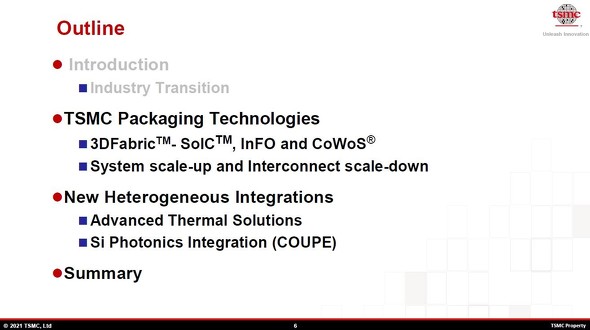

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)前回は、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」の概要を解説した。今回は、「SoIC」の開発ロードマップをご説明する。

ベースとなるのはSoC(System on a Chip)の微細化ロードマップだ。SoCの製造プロセスでは2018年に7nm(N7)世代の量産が、2020年に5nm(N5)世代の量産が始まった。2022年には3nm(N3)世代の量産を始める計画である。SoICのロードマップは、チップとウエハーを積層する「CoW(Chip on Wafer)」のロードマップと、ウエハーとウエハーを積層する「WoW(Wafer on Wafer)」のロードマップを用意した。

SoCと「SoIC」の開発ロードマップ[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

SoCと「SoIC」の開発ロードマップ[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)CoWは、上側のシリコンダイ(トップダイ)と下側のシリコンダイ(ボトムダイ)ともに、7nm(N7)世代および6nm(N6)世代で2021年に量産を始めたところである。2022年にはトップおよびボトムともに、5nm(N5)世代の量産を始める。2023年末には、トップダイの最先端プロセスが3nm(N3)世代に移行する。

WoWはCoWに比べると量産導入の時期が遅い。2022年に、7nm(N7)世代のプロセスと深い溝形キャパシタ(DTC:Deep Trench Capacitor)の組み合わせで量産を始める。2023年末までには、5nm(N5)世代へと微細化を進める。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待