EE Times Japan >

LSI >

3次元集積化技術「SoIC」の開発ロードマップ:福田昭のデバイス通信(339) TSMCが開発してきた最先端パッケージング技術(12)(2/2 ページ)

» 2021年12月23日 11時30分 公開

[福田昭,EE Times Japan]

3次元集積の接続密度は年率2倍で急速に上昇

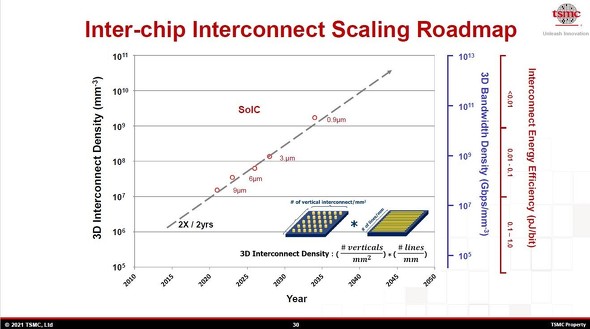

講演では、「SoIC」技術による3次元集積が、体積当たりの相互接続数(接続密度)を急速に増やしていくとの予測を示した。シリコンダイを積層したときの接続ピッチを詰めることで、面積当たりの接続数を増加させる。体積当たりの接続数は年率2倍で急増すると予測する。2020年には立方ミリメートル当たりの接続数は10の7乗(1000万)だった。それが2035年には、10の9乗(10億)と15年で100倍になると見込む。

体積当たりの接続密度(左縦軸)と体積当たりの帯域幅(右縦軸)、ビット当たりの接続エネルギー(右縦軸)の変化(2015年〜2045年)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

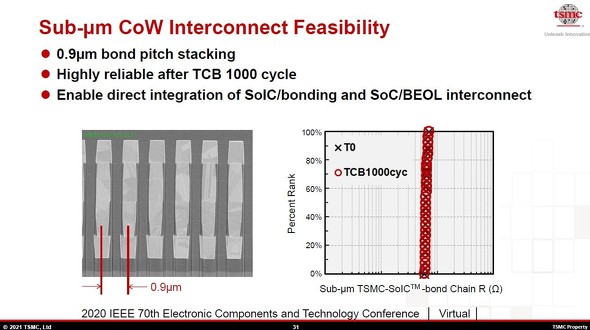

体積当たりの接続密度(左縦軸)と体積当たりの帯域幅(右縦軸)、ビット当たりの接続エネルギー(右縦軸)の変化(2015年〜2045年)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)接続ピッチの短縮に寄与するのが、バンプなしでシリコンダイの表面同士を接続する「ハイブリッド接合(Hybrid Bonding)」技術である。シリコンダイの表面には銅(Cu)電極と絶縁膜が形成してあり、Cu電極同士の位置を合わせて張り合わせる。貼り合わせの対には、「CoW(Chip on Wafer)」と「WoW(Wafer on Wafer)」がある。講演では、電極ピッチが0.9μmと非常に短い「CoW」の試作例を示していた。

「CoW(Chip on Wafer)」のハイブリッド接合。左は接合部の断面観察像。電極の接続ピッチは0.9μmと短い。右は1000サイクルの温度サイクル試験の前後で接合鎖の抵抗値を測定した結果[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「CoW(Chip on Wafer)」のハイブリッド接合。左は接合部の断面観察像。電極の接続ピッチは0.9μmと短い。右は1000サイクルの温度サイクル試験の前後で接合鎖の抵抗値を測定した結果[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)試作したCoWの接合は、温度サイクル試験(1000サイクル)を経ても抵抗値の上昇がみられなかった。0.9μmと短いピッチは、接続密度のロードマップでは2035年に対応する。言い換えると、2035年までの接続密度向上は実現性が見えていることになる。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR