HARエッチングとナノスケールパターニングで実現するメモリロードマップ:ラムリサーチ(2/3 ページ)

HARエッチングの問題に対する解決策

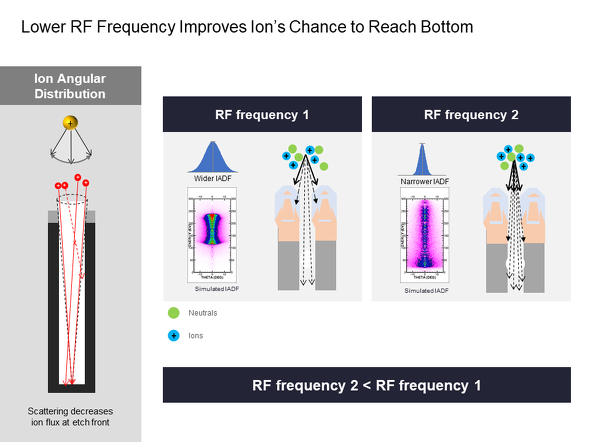

プラズマを生成するシステム、特にRFサブシステムに着目することで解決策が見つかります。RFの周波数を下げること、すなわち、その半周期とイオンが(イオンを加速する)高電圧シース内を通過する時間を近づけることで、投入されたRFパワーに対するイオンのピークエネルギーは最大になります。RFの周波数を下げ、イオンのピークエネルギーを高めることは、イオンの角度分布を狭めることにつながり、イオンは、よりHAR構造の底部に到達しやすくなります(図3)。

従って、ハードウェアの設計面では、RFの低周波数化、高出力化、(パルス駆動の)低デューティ比化への移行が重要な課題になります。

ハードウェアの設計を変更してもなお、通常、酸化膜-窒化膜-酸化膜-窒化膜(ONON)から成る128、あるいはそれ以上の積層膜を貫通する、深さ6.9μmのチャネルホールをエッチングすることは、依然として非常に困難な技術です。

そこでラムリサーチは必要なエッチング深さを実現する、異なるアプローチをテストしています。まず、準備段階としてチャネルホールを、例えば5μm程度の深さまでエッチングし、その後、横方向への不要なエッチングを防止する、保護ライナーを側壁に成膜します。そして後続のステップでチャネルホールを6.9μmまでエッチングするというものです。

ライナーを追加することで、CDを拡げることなく、さらに1μmのエッチングが可能になります。まだ大幅な最適化が必要ではありますが、実験結果はこのプロセスがより狭く、より深いホールをエッチングする有望な手法であることを示しています。

パターニングの課題と同時最適化技術

ロジックやメモリのパターニングは、コスト削減や性能向上を目指すチップメーカーにとって最優先事項といえます。現在は、最小限の誤差で、より微細な構造へスケールダウンすることが極めて重要です。その誤差はエッジ配置誤差(EPE:Edge Placement Error)で測ることができます。

例えばホールの位置合わせでは、ラインエッジラフネス(LER)、スキャナのオーバーレイ誤差、EUV露光の確率的な変動によって引き起こされる局所的なCDのばらつきなど、いくつものばらつきの問題に直面します。デバイスの設計は、ばらつきの平均値よりも、むしろ極値によってしばしば制限されます。こうしたばらつきへの対処は、最悪のシナリオを許容するようにした場合、ロジック・バックエンド面積の50%にも及ぶ可能性があり、製造コストを大幅に増加させます。

ばらつきを抑制する方法の一つに、プロセス間の同時最適化があります。これは通常、リソグラフィで生じた誤差をエッチングで補正することを意味します。同時最適化を実現するためにはウエハー面内および、ウエハー間のエッチング性能を、より効果的に制御可能とする、適切なチューナビリティ(制御性)を装置に持たせる必要があります。

エッチング中にウエハーがさらされるプラズマのコンディションやガス分布は常に変化しています。温度の変化を制御できるようになれば、プロセスにチューナビリティを持たせることができ、チャンバー内に起因するばらつきだけでなく、リソグラフィによるばらつきも補正できるようになります。

このように温度を制御し、それによってエッチング速度を制御する方法の一つに、ウエハーを保持するチャック上に調整可能な温度ゾーンを設けてウエハーの温度を制御する方法があります。チャックは、2000年代初頭のシングルゾーンから、デュアルゾーン、ラジアル・マルチゾーン、そして近年ではラムリサーチの「Hydra Uniformity System」のノンラジアル・マルチゾーンへと10年以上にわたる進化を遂げています。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待