東京工大、溶液法で高性能のpチャネルTFTを開発:既存物質を組み合わせ長所生かす

東京工業大学は、溶液法を用いて、優れた半導体特性を有する「pチャネル薄膜トランジスタ(TFT)」の開発に成功した。新規開発の材料ではなく、既存の物質同士をうまく組み合わせることによって実現した。

IGZO-TFTと組み合わせ、高性能CMOSとして機能

東京工業大学元素戦略研究センターの金正煥(キム・ジョンファン)助教、細野秀雄栄誉教授らは2022年1月、溶液法を用いて、優れた半導体特性を有する「pチャネル薄膜トランジスタ(TFT)」の開発に成功したと発表した。新規開発の材料ではなく、既存の物質同士をうまく組み合わせ、それぞれの長所を生かすことによって実現した。

n型半導体は、アモルファス酸化物半導体「InGaZnO(IGZO)」を用いたTFTが、高精細液晶ディスプレイなどで実用化されている。IGZO-TFTは、シリコン系TFTに比べ、「キャリア移動度が10倍以上高く、大面積の薄膜を低温プロセスで作製できる」などの特長がある。

こうしたことから、論理回路への応用も期待されているが、そのためにはIGZO-TFTと組み合わせて用いるp型半導体の性能を向上させる必要がある。半導体の特性として、特に重要となるのが、優れた「キャリア制御性」と「キャリア移動度」である。しかし、これらをクリアできる新たな材料は、まだ探し出せていないという。

そこで研究チームは、既存の物質同士をうまく組み合わせることによって、優れた半導体特性を実現することにした。そこで着目したのが金属ハロゲン化物(ヨウ化物)半導体である。今回は、PEA2SnI4(フェニチルアンモニウムイオン、スズ、ヨウ素からなる2次元構造化合物)と、FASnI3(ホルムアミジウムイオン、スズ、ヨウ素からなる3次元構造化合物)を用いた。

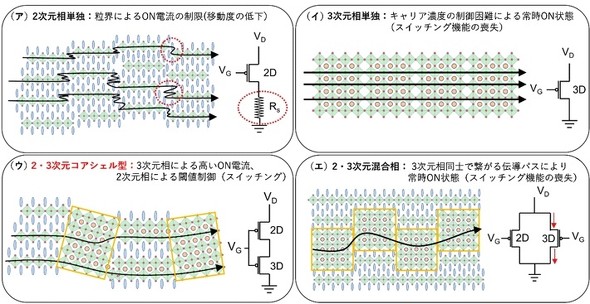

いずれもペロブスカイト型の結晶構造を持つ物質であるが、その特性は異なる。PEA2SnI4はキャリア制御性に優れるが、電気抵抗は高くキャリア移動度が低い。これに対しFASnI3は、キャリア移動度は高いが、キャリア濃度の制御が難しいという。今回はこの2つの物質を混在させ、微細構造を制御することにより、両者の長所を生かすことにした。

具体的には、キャリアが3次元相と2次元相の両方を通過して電流が流れる構造(コア-シェル構造)を作ることが必要と考えた。その上で3次元相が2次元相によって完全に隔離されているような構造になるよう、製膜の作製条件を設定した。

上図は2次元および3次元ペロブスカイトTFTが抱えている現状の問題点、左下は2/3次元コア−シェル型複合相からなるTFT、右下は2/3次元相の混合層からなるTFT[クリックで拡大] 出所:東京工業大学

上図は2次元および3次元ペロブスカイトTFTが抱えている現状の問題点、左下は2/3次元コア−シェル型複合相からなるTFT、右下は2/3次元相の混合層からなるTFT[クリックで拡大] 出所:東京工業大学実験では、PEA2SnI4とFASnI3を含む溶液を塗布した後、加熱・真空処理を行って薄膜を作製した。そして、「PEA2SnI4とFASnI3の比率」や、「添加物の有無」「添加物の量」などが、生成する薄膜にどのような影響を与えるか検証した。

PEA2SnI4とFASnI3を1対6の比率で混ぜた溶液に、微量(2mol%)のフッ化スズ(SnF2)を添加したところ、コア−シェル構造が得られた。TFTの特性からは、約5Vのしきい値電圧でスイッチングをしていることが分かった。ところが、SnF2添加剤を用いない場合、しきい値電圧は約90Vと極めて高くなった。

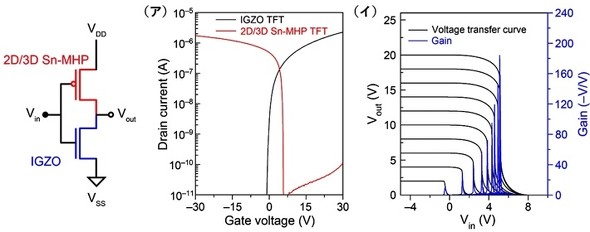

さらに研究チームは、従来のnチャネルIGZO-TFTと、開発したpチャネル2/3次元ペロブスカイトTFTを組み合わせてCMOSインバーターを作製した。これを評価したところ、PEA2SnI4とFASnI3の比率を1対9にすると、25cm2/Vsという極めて高い電界効果移動度を得られることが分かった。しかも、このCMOSインバーターからは、約180V/V(VDD=20V)という極めて高いゲインが得られたという。

研究チームは今後、研究成果の早期実用化を目指し、大気中における安定性などペロブスカイト型ハロゲン化物特有の課題解決に向けて、産学共同で取り組む考えである。

関連記事

低下した全固体電池の性能を加熱処理で大幅改善

低下した全固体電池の性能を加熱処理で大幅改善

東京工業大学は、東京大学や産業技術総合研究所、山形大学らと共同で、低下した全固体電池の性能を、加熱処理だけで大幅に改善させる技術を開発した。電気自動車用電池などへの応用が期待される。 東京工大ら、SOT-MRAM素子の原理動作実証に成功

東京工大ら、SOT-MRAM素子の原理動作実証に成功

東京工業大学と米国カリフォルニア大学ロサンゼルス校を中心とした国際研究チームは、トポロジカル絶縁体と磁気トンネル接合(MTJ)を集積したスピン軌道トルク磁気抵抗メモリ(SOT-MRAM)素子を試作し、読み出しと書き込みの原理動作を実証した。 レドックス・フロー熱電発電で発電密度を1桁向上

レドックス・フロー熱電発電で発電密度を1桁向上

東京工業大学の研究グループは、排熱源を冷却しながら発電を行う「レドックス・フロー熱電発電」で、従来に比べ発電密度を1桁以上高くすることに成功した。 光照射で結晶中を移動する酸化物イオンを直接観測

光照射で結晶中を移動する酸化物イオンを直接観測

筑波大学と東京工業大学、広島工業大学の研究グループは、特殊なセラミックス材料に光照射し、室温環境で酸化物イオンを瞬時に移動させ、それを直接観測することに成功した。研究成果は、光を用いた燃料電池や二次電池などの開発に、新たな展開をもたらすと期待されている。 スマホでAI処理を行うプロセッサアーキテクチャ

スマホでAI処理を行うプロセッサアーキテクチャ

東京工業大学は、高度なAI処理をスマートフォンなどで実行できる「プロセッサアーキテクチャ」を開発した。試作したチップの実効効率は最大26.5TOPS/Wで、世界トップレベルだという。 量子センサーのスピン情報、電気的読み出しに成功

量子センサーのスピン情報、電気的読み出しに成功

東京工業大学と産業技術総合研究所(産総研)の共同研究グループは、ダイヤモンド量子センサーのスピン情報を、電気的に読み出すことに成功した。感度が高い集積固体量子センサーの実現が期待される。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 次世代パワー半導体 「期待の5材料」の現在地

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- パワー停滞も光デバイス堅調、三菱電機の半導体部門