PSB技術を用いたチップレット集積技術を開発:広帯域接続と大規模集積が可能に

東京工業大学とアオイ電子らによる共同研究チームは、広帯域のチップ間接続性能と集積規模の拡大を可能にするチップレット集積技術「Pillar-Suspended Bridge(PSB)」を開発したと発表した。

産学共同で研究開発/産業化を目指すコンソーシアムも設立

東京工業大学科学技術創成研究院未来産業技術研究所の栗田洋一郎特任教授とアオイ電子らによる共同研究チームは2022年10月、広帯域のチップ間接続性能と集積規模の拡大を可能にするチップレット集積技術「Pillar-Suspended Bridge(PSB)」を開発したと発表した。

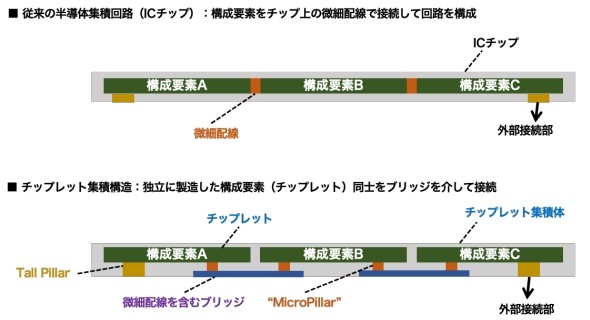

素子の微細化や高集積化によって性能向上を実現する「ムーアの法則」が、物理的な限界を迎えようとしている中、近年はチップレット集積技術が注目されている。ICチップの集合体で主要なシステムを構成する技術で、異なる機能や構造のICチップを大規模に集積することができる。

今回開発したPSB技術は、チップレットとシリコンブリッジの接続を「MicroPillar」と呼ぶ柱状金属で行う。チップレット集積体はブリッジとともにモールド樹脂封止されている。外部電極と接続するのは、シリコンブリッジ側のモールドを貫通する「Tall Pillar」である。また、「All Chip-last」と呼ぶ製造プロセスにより、高い接合精度と作業中のダイシフトを抑制できるという。

こうした構造にしたことで、チップ間接続密度や電気特性の向上、外部接続配線の高周波特性や放熱性能の改善などが可能となる。しかも、ブリッジの配線種類を選択することができ、集積規模を拡大する時に歩留まりを気にする必要もないという。

PSB構造はシンプルで合理的な構造であり、Fan-Out機能を有する配線層を接続すれば、チップレット集積パッケージや大規模なチップレット集積システムを構成することができる。今回は、PSB技術を実証するため試作機を用いて、その実現性も実証した。

なお、2022年10月1日付で、「チップレット集積プラットフォーム・コンソーシアム」が設立された。今回の研究を含むチップレット集積プラットフォーム技術全般を対象に、製造技術/要素技術からアプリケーションに至るまでの研究開発とその産業化を狙いに活動する。

コンソーシアムメンバーは東京工業大学の他、大阪大学(菅沼克昭特任教授/大阪大学名誉教授)や東北大学(福島誉史准教授)を中心に、アオイ電子、アピックヤマダ、アルバック、青梅エレクトロニクス、奥野製薬、住友電気工業、住友ベークライト、太陽インキ製造、トーヨーケム、フォームファクター、マクセル、リンテック、FICT、他3社が参加。協賛企業として、ディジタルメディアプロフェッショナル、トッパン・テクニカル・デザインセンター、NSCore、他13社が参加を表明している(2022年9月現在)。

関連記事

産総研ら、表面弾性波で単一電子を高い効率で移送

産総研ら、表面弾性波で単一電子を高い効率で移送

産業技術総合研究所(産総研)や東京工業大学らによる研究グループは、表面弾性波の孤立パルスを発生させる技術を開発するとともに、この技術を用い単一電子を高い効率で移送することに成功した。量子コンピュータにおける量子情報の移送手段として、その応用が期待される。 Crハライド系物質でスピン流の整流効果を発見

Crハライド系物質でスピン流の整流効果を発見

東京工業大学と千葉大学は、磁性絶縁体のCrハライド系物質にギガヘルツからテラヘルツ帯の電磁波を印加すると、スピン流の整流効果が生じることを理論的に解明した。しかも、スピン流の強度はこれまでの予測値に比べ、約2桁大きくなることも分かった。 全固体リチウム電池の界面抵抗を2800分の1に

全固体リチウム電池の界面抵抗を2800分の1に

東京工業大学と東京大学の研究グループは、全固体リチウム電池において硫化物固体電解質と電極材料の界面に化学反応層が形成されると、極めて高い界面抵抗が生じることを解明した。この界面に緩衝層を導入すれば、界面抵抗は2800分の1に低減され、電池は安定動作することを実証した。 産総研、次世代コンピューティング基盤戦略を策定

産総研、次世代コンピューティング基盤戦略を策定

産業技術総合研究所(産総研)エレクトロニクス・製造領域およびTIA推進センターは、次世代コンピューティングのハードウェア開発において、日本が取り組むべき戦略を策定し、その概要を公開した。 東京工大、ミリ波帯フェーズドアレイ無線機を開発

東京工大、ミリ波帯フェーズドアレイ無線機を開発

東京工業大学は、無線電力伝送と無線通信に同時対応する「ミリ波帯フェーズドアレイ無線機」を開発した。ビームステアリングにより、電力と通信信号を同時に受信することができるため、無線電力伝送と無線通信の長距離化や広角化が可能になるという。 絶縁体と金属を繰り返すイットリウム化物薄膜作製

絶縁体と金属を繰り返すイットリウム化物薄膜作製

東京工業大学らの共同研究グループは、イットリウム酸水素化物(YOxHy)のエピタキシャル薄膜を作製し、紫外光照射と加熱を行うことで「絶縁体」と「金属」の状態を繰り返し変換させることに成功した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

従来の半導体集積回路とチップレット集積構造の比較 出所:東京工業大学

従来の半導体集積回路とチップレット集積構造の比較 出所:東京工業大学 PSBによるチップレット集積構造のコンセプト実証サンプルの外観 出所:東京工業大学

PSBによるチップレット集積構造のコンセプト実証サンプルの外観 出所:東京工業大学

上図はPSBモジュールの外部接続構造図、下図は大規模チップレット集積のイメージ図 出所:東京工業大学

上図はPSBモジュールの外部接続構造図、下図は大規模チップレット集積のイメージ図 出所:東京工業大学