半導体の微細化は2035年まで続く 〜先端ロジックのトランジスタと配線の行方:湯之上隆のナノフォーカス(55)(2/5 ページ)

半導体の微細化は2035年まで続く

EUVを使った半導体の微細化のロードマップは、既に2020年のIEDMでimecが示している(図3)。それによると半導体の微細化は、次の4段階で進む。

1) 0.33NAのEUVによるシングル露光 → 32〜28nmピッチ

2) 0.33NA EUV+マルチパターニング → 24〜20nmピッチ

3) 0.55NA(High NA)EUVのシングル露光 → 18nmピッチ位以降

4) 0.55NA(High NA)EUV+マルチパターニング → さらに微細なピッチ

図3:0.33 NAと0.55 NAのEUVを使った微細化のロードマップ[クリックで拡大] 出所:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020.のスライドに筆者加筆(赤枠と矢印および番号)

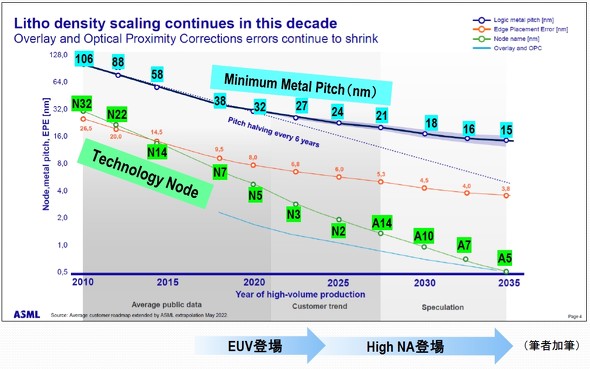

図3:0.33 NAと0.55 NAのEUVを使った微細化のロードマップ[クリックで拡大] 出所:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020.のスライドに筆者加筆(赤枠と矢印および番号)このようなシナリオで、半導体の微細化が進んだ場合、スローダウンはしつつも、2035年まで半導体の微細化が続くことを、2022年のVLSIシンポジウムでASMLが示した(図4)。

図4:半導体の微細化はスローダウンしつつも2035年まで続く[クリックで拡大] 出所:Michael Lercel (ASML), “Lithography and Patterning for 3nm node and beyond”, SemiconWest 2022.のスライドに筆者加筆

図4:半導体の微細化はスローダウンしつつも2035年まで続く[クリックで拡大] 出所:Michael Lercel (ASML), “Lithography and Patterning for 3nm node and beyond”, SemiconWest 2022.のスライドに筆者加筆現在最先端のTechnology NodeはN5で、最も微細な配線のピッチは32nmである。恐らく、High NAは、2025年の「N2」(微細配線ピッチ24nm)辺りから登場すると思われる。そして、2035年にはそのTechnology Nodeが「A5」となり、微細配線ピッチは15nmになることが示されている。なお、Technology Nodeの“A”はオングストローム(Å)を意味するものと思われる。

ことし2022年から13年後の2035年まで半導体の微細化は続く。もちろんこれはHigh NAが計画通りに実用化されたらの話ではあるが、この図3が、2022年のVLSIシンポジウムの中で、筆者にとって最も印象的なスライドとなった。

ロジック半導体のトランジスタのロードマップ

2019年にEUVが微細化の扉をこじ開けた。そして、High NAが登場すれば、半導体の微細化は2035年まで続く。その微細加工技術を使って、先端ロジック半導体のトランジスタや微細配線は、どのように進化を遂げるのだろうか?

図5は、2020年のIEDMでimecが示したロジック半導体のトランジスタや微細配線のロードマップである。トランジスタ構造は、3nmから2nmにかけてFinFETからGate-All-Around(GAA)構造のNanosheetsに変わる。そして、フォークのような形状のForksheetsを経て、1.5nm以降にpMOSとnMOSを縦に形成するComplementary FET(CFET)となることが示されている。さらに1nmとそれ以降については、2D channelsという全く異なるトランジスタ構造になると予測している。

図5:先端ロジックのトランジスタや配線のロードマップ(imec)[クリックで拡大] 出所:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020.

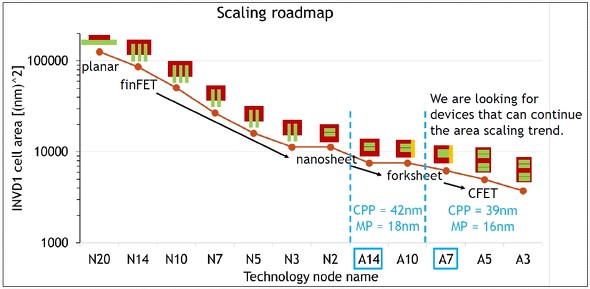

図5:先端ロジックのトランジスタや配線のロードマップ(imec)[クリックで拡大] 出所:Sri Samavedam(imec), “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”, IEDM2020.ここで、CFETは、(筆者の記憶によれば)2017年頃からimecが発表し始めたCMOSであるが、このような複雑な構造をどうやって形成するのか、このCMOSを数十〜数百億個以上集積したロジック半導体は本当に動作するのか、などの疑問を持っていた。しかし、2017年以降もimecは毎年、CFETの発表を継続してきた。ことしのVLSIシンポジウムでもimecは、N3からNanosheetsになり、Forksheetsを経て、「A7」からCFETになるという新たなロードマップを発表した(図6)。

図6:先端ロジックのトランジスタのロードマップ(imec)[クリックで拡大] 出所:Pieter Schuddinck(imec), “PPAC of sheet based CFET configurations for 4 track design with 16nm metal pitch”, VLSI2022, T10-2.

図6:先端ロジックのトランジスタのロードマップ(imec)[クリックで拡大] 出所:Pieter Schuddinck(imec), “PPAC of sheet based CFET configurations for 4 track design with 16nm metal pitch”, VLSI2022, T10-2.そして、とうとう、そのCFETが、TSMCのトランジスタのロードマップに記載された(図7)。研究機関であるimecがロードマップにCFETを掲載していることと、実際にファウンドリーとしてロジック半導体の大量生産を行っているTSMCが自社のロードマップにCFETを乗せたこととは意味合いが大きく異なる。筆者は、TSMCが、GAAの次にCFETを採用する覚悟を決めたのだろうと感じた。その時期は、imecのロードマップを参考にすればA7からで、2030年以降になると思われる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」