3nmの増産目指すTSMCの課題と現状:ASMLの最先端装置の導入も加速(2/2 ページ)

TSMCの3nm遅延の背景

Hosseini氏は、「TSMCの3nm導入および製造拡大に遅延が生じていたのは、ASMLのEUV(極端紫外線)リソグラフィによるマルチパターニングを導入する必要があったからだ」と指摘する。

「EUVマルチパターニングはコストが高いため、EUVは費用対効果の面で魅力を失っていたが、EUVマルチパターニングのレイヤー数を最小限に抑えられるよう設計ルールを緩和した結果、ダイサイズが大幅に拡大した。真の3nmノードが拡大していくのは、スループット向上を実現したASMLのEUVシステム『NXE:3800E』が2023年後半に利用できるようになってからになるだろう」(Hosseini氏)

Hosseini氏によると、NXE:3800Eは、EUVマルチパターニングの全体コストを削減することにより、ウエハーのスループットを既存の「NXE:3600D」と比べて約30%向上させることが可能だという。

同氏はレポートの中で、「TSMCは、より多くの顧客向けに、N3Eをはじめとする3nmノードの派生プロセスの生産を拡大すべく、2024年前半にNXE:3800Eの導入を加速する予定だ」と述べている。

TSMCは、顧客であるNVIDIAからリソグラフィ関連のサポートを受けている。

C.C. Wei氏は、「(計算リソグラフィを高速化するNVIDIAのソフトウェアライブラリ)『cuLitho』ソフトウェア/ハードウェアによって、コストの高い処理をNVIDIA GPUに移行させることで、TSMCがILT(Inverse Lithography Technology)や深層学習を展開できるようサポートを提供する」と述べる。

Bank of Americaのリサーチアナリストを務めるBrad Lin氏は、「TSMCは最近、2nmプロセス以降の製造においてNVIDIAとSynopsys、ASMLとの協業を発表している。TSMCは現在、そのグループの中で唯一のファウンドリーだ」と述べている。

2nm世代の生産は2025年にもスタート

TSMCは、次世代のノードである「N2」の生産を2025年にも開始する予定だ。

C.C. Wei氏は、「N2には、顧客から高い関心が寄せられていて、顧客の関与も多い」と語る。「当社の2nm技術は、トランジスタ密度とエネルギー効率の両面で業界最先端のプロセスノードとなり、将来にわたり、当社の技術リーダーシップが拡大されることになるだろう」(同氏)

現在のチップ在庫調整は、TSMCが3カ月前に予測した水準よりも高く、ことし(2023年)の第3四半期にまで及ぶ可能性があるという。その結果、TSMCは、2023年の売上高がほぼ10年ぶりに減少する可能性があると予測した。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

TSMCの23年Q1決算、前四半期比で大幅減益に

TSMCの23年Q1決算、前四半期比で大幅減益に

TSMCが2023年1〜3月期の決算を発表した。売上高は5086億3000万ニュー台湾ドルで、前年同期比で3.6%増、前四半期比では18.7%減。純利益は2069億ニュー台湾ドルで前四半期比では30%の大幅減となった。 ここが変だよ 日本の半導体製造装置23品目輸出規制

ここが変だよ 日本の半導体製造装置23品目輸出規制

2023年3月、経済産業省は、半導体製造装置など23品目を輸出管理の対象として追加する方針を固めた。だが、ここで対象とされている製造装置、よくよく分析してみると、非常に「チグハグ」なのである。何がどうおかしいのか。本稿で解説したい。 計算リソグラフィを40倍高速化するAIライブラリ

計算リソグラフィを40倍高速化するAIライブラリ

NVIDIAは、計算リソグラフィ(Computational Lithography)の高速化に向けたAIライブラリを発表した。1枚のフォトマスクの作成時間が、2週間から8時間に、大幅に短縮されるとする。TSMCは2023年6月から導入するという。 TSMC熊本工場向けに、半導体材料拠点を新設へ

TSMC熊本工場向けに、半導体材料拠点を新設へ

エア・ウォーターは2023年2月28日、熊本県菊池郡大津町にエレクトロニクス関連事業のグループ複合拠点を新設すると発表した。TSMCの熊本工場建設に伴い伸長する半導体材料需要を獲得する狙いだ。 「OTを止めるな」 半導体業界に必須のサイバー攻撃対策

「OTを止めるな」 半導体業界に必須のサイバー攻撃対策

半導体工場を対象としたサイバー攻撃の急増を受け、SEMIはセキュリティ規格「SEMI E187」を策定した。TXOne Networks Japanに、製造業/半導体業界のセキュリティ対策について聞いた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

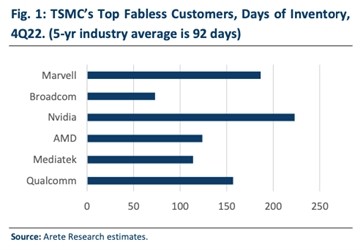

TSMCの主要顧客と、2022年第4四半期における在庫日数(業界における5年平均は92日だという) 出所:Arete Researchの推測による

TSMCの主要顧客と、2022年第4四半期における在庫日数(業界における5年平均は92日だという) 出所:Arete Researchの推測による