EE Times Japan >

先端技術 >

ナノシート酸化物半導体を用いたトランジスタ開発:原子層堆積法で均一にナノ薄膜形成

東京大学と奈良先端科学技術大学院大学の共同研究グループは、低温で形成できるナノシート酸化物半導体をチャネル材料に用いて、高性能かつ高信頼のトランジスタを開発した。

» 2023年06月12日 10時30分 公開

[馬本隆綱,EE Times Japan]

IGOナノシートをゲートで覆ったGate-All-Around構造を提案

東京大学生産技術研究所の小林正治准教授と、奈良先端科学技術大学院大学物質創成科学領域の浦岡行治教授らによる共同研究グループは2023年6月、低温で形成できるナノシート酸化物半導体をチャネル材料に用いて、高性能かつ高信頼のトランジスタを開発したと発表した。

先端半導体は、さらなる高集積化や高機能化が求められている。こうした中で、三次元構造など半導体の高集積化を進めていくうえで期待されているのが「酸化物半導体」である。酸化物半導体は、既にフラットパネルディスプレイで用いられてきた。この材料を半導体集積回路へ応用するには、均一なナノ薄膜の製膜技術が重要になるという。

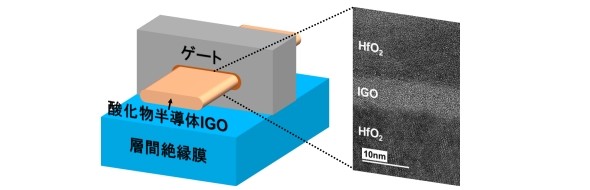

研究グループは今回、原子層堆積法を用い酸化物半導体のナノ薄膜を形成する技術を開発した。具体的には、In2O3とGa2O3を原子層ごと、交互に成膜をしてInGaO(IGO)のナノ薄膜を形成した。このナノシートIGOをチャネル材料とするプレーナ型トランジスタを試作した。

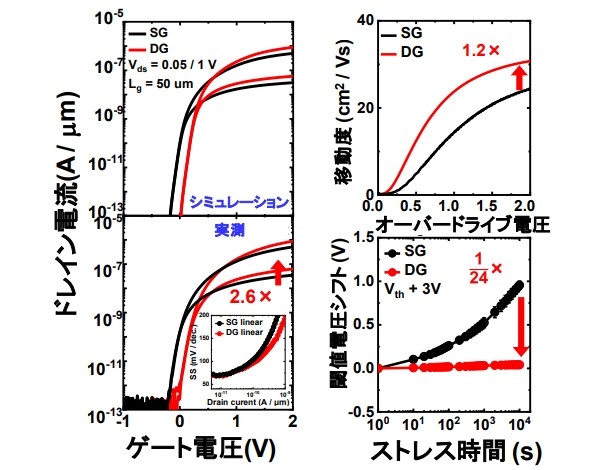

この試作品を用いて、移動度としきい値シフトにおけるトレードオフの関係性について解明した。その上で、トレードオフの課題を解決するため、新たにIGOナノシートをゲートで覆った「Gate-All-Around構造」を開発した。新たな構造を採用したことで、「ノーマリーオフ動作」や「プレーナ型に対して駆動電流が2.6倍向上」「移動度は1.2倍向上」「しきい値電圧シフトの大幅な低減」を実現したという。

関連記事

東京大、酸化物素子で磁気抵抗比を10倍以上に

東京大、酸化物素子で磁気抵抗比を10倍以上に

東京大学は、単結晶酸化物を用いて作製した強磁性体/半導体/強磁性体構造の横型2端子素子で、従来の10倍以上となる磁気抵抗比が得られたと発表した。この構造を用いて試作した3端子スピントランジスタ素子では、ゲート電圧によって電流を変調させることにも成功した。 RaaS、先端半導体設計プラットフォームを開発へ

RaaS、先端半導体設計プラットフォームを開発へ

東京大学やアドバンテストなどが組合員として活動する「先端システム技術研究組合(RaaS:ラース)」は、2023年4月1日より「次世代先端半導体設計プラットフォーム」の研究開発を始めた。 多数のベンゼン環からなる「ポリアセン」を合成

多数のベンゼン環からなる「ポリアセン」を合成

東京大学の研究グループは、多数のベンゼン環が直線状に連結した「ポリアセン」を合成することに成功した。太陽電池やナノデバイスなどへの応用を目指す。 グラファイト基板上に半導体ナノ量子細線を作製

グラファイト基板上に半導体ナノ量子細線を作製

京都大学や東京大学らの研究グループは、約1nmという厚みと幅で、長さが1μmを超える半導体の「ナノ量子細線」を作製したと発表した。この量子細線パターンは、原子スケールでチューリング機構が起こり、自発的に形成された可能性が高いという。 反強磁性体で「トポロジカルホール効果」を実証

反強磁性体で「トポロジカルホール効果」を実証

東京大学は、磁化を持たない反強磁性体において、「トポロジカルホール効果」を実証することに成功した。「新しい磁気情報媒体として活用できる可能性がある」とみている。 東京大ら、フィルム状有機半導体センサーを開発

東京大ら、フィルム状有機半導体センサーを開発

東京大学とファームシップは、カリウムイオンを安定的に計測できる「フィルム状の有機半導体センサー」を開発した。このセンサーを用い、レタスの栽培実験に成功した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR

試作したナノシート酸化物半導体トランジスタの模式図と透過型顕微鏡による断面像 出所:東京大学他

試作したナノシート酸化物半導体トランジスタの模式図と透過型顕微鏡による断面像 出所:東京大学他 ナノシート酸化物半導体トランジスタの電気特性シミュレーション結果(左上)と実測結果(左下)。プレーナ型トランジスタと比較した移動度(右上)とバイアスストレスしきい値電圧シフト(右下)のグラフ 出所:東京大学他

ナノシート酸化物半導体トランジスタの電気特性シミュレーション結果(左上)と実測結果(左下)。プレーナ型トランジスタと比較した移動度(右上)とバイアスストレスしきい値電圧シフト(右下)のグラフ 出所:東京大学他