超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP:福田昭のデバイス通信(435) 2022年度版実装技術ロードマップ(59)(2/2 ページ)

FO-WLPはマルチチップの格納が容易

FO-WLPの組み立て工程には、いくつかのバリエーションがある。まず、キャリアにシリコンダイを配置してから再配線層(RDL)と外部端子を形成する「チップファースト(Chip First)」と、キャリアに再配線層を形成してからシリコンダイを搭載する「RDLファースト(RDL First)」に分かれる。さらに「チップファースト」には、シリコンダイの回路面を下にして載せる「フェースダウン(Face Down)」と回路面を上にして載せる「フェースアップ(Face Up)」がある。

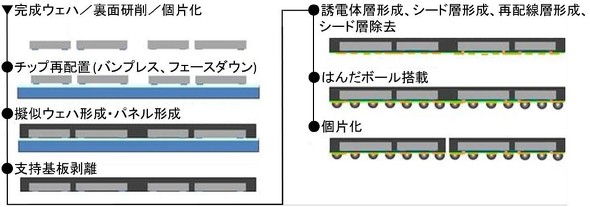

以下は、初期に開発されて現在でも標準的なFO-WLPである「チップファースト」かつ「フェースダウン」の組み立て工程を説明しよう。はじめは既に述べたように、回路を形成済みのシリコンウエハーを裏面から所望の厚さになるまで研削し、個々のシリコンダイに切り離す。それからキャリアにシリコンダイ(チップ)をフェースダウンで再配置する。ここで重要なのは、マルチチップの格納を前提にした配置(図面では2枚のチップを1個のFO-WLPに格納)が可能なことだ。WL-CSPはシングルダイが前提なので、パッケージに収容できる回路の規模を大きくできない。FO-WLPは2枚〜3枚といったチップを横に並べて1個のパッケージに組み立てられるので、大規模な回路を収容しやすい。

キャリアの表面にはあらかじめ粘着性フィルムが貼ってある。フェースダウンで置かれたシリコンダイはこのフィルムに貼り付く。次にモールド樹脂でシリコンダイの周囲を覆って疑似ウエハーを作成する。続いて疑似ウエハーからキャリアを剥がす。するとシリコンダイの回路面が露出するので、回路面に再配線層(RDL)を形成し、外部端子(はんだボール)を載せる。最後に個々のパッケージに切り離す。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

表面実装工程の省エネに寄与する低融点の鉛フリーはんだ

表面実装工程の省エネに寄与する低融点の鉛フリーはんだ

今回は、第2章第6節第6項「2.6.6 接合材料」から、「SMT(Surface Mount Technology)における接合材料の現状と課題」の概要を紹介する。 エレクトロニクスの進化を後押しする接合技術

エレクトロニクスの進化を後押しする接合技術

JEITAが発行する「2022年度版 実装技術ロードマップ」を紹介するシリーズ。今回から、第2章第6節第6項「2.6.6 接合材料」の概要を紹介していく。 コンピューティングと計測・センシングの限界を打破する量子技術(前編)

コンピューティングと計測・センシングの限界を打破する量子技術(前編)

今回は、第2章第6節第5項「2.6.5 量子技術」の内容を簡単に説明する。 複数のガス分子を選択的に検出する「におい」センサー

複数のガス分子を選択的に検出する「におい」センサー

前回に続き、「におい」を定量的に評価する手法を取り上げる。今回は「成分濃度表示法(機器分析法)」を紹介する。 味覚の定量的なセンシングとその巨大な意義

味覚の定量的なセンシングとその巨大な意義

「味覚」の概要を取り上げるシリーズの続き。本稿では、味覚を定量的に検出する「味覚センサー」とその意義について解説する。 PHS内蔵の情報端末で始まった日本の「スマートフォン」(1996年〜1997年)

PHS内蔵の情報端末で始まった日本の「スマートフォン」(1996年〜1997年)

今回は、日本で初めてのスマートフォンをご紹介する。具体的には、日本独自の簡易型携帯電話システム「PHS(Personal Handy-phone System)」(当初の呼び名は「ピーエイチエス」、後の呼び名は「ピッチ」)と携帯型情報端末(PDA)を融合したデバイスである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増