超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP:福田昭のデバイス通信(435) 2022年度版実装技術ロードマップ(59)(1/2 ページ)

引き続き、各種パッケージ技術の動向を紹介する第3章第3節を取り上げる。今回から「3.3.2.2 FO-WLP、FO-PLP、部品内蔵基板」の概要を紹介する。

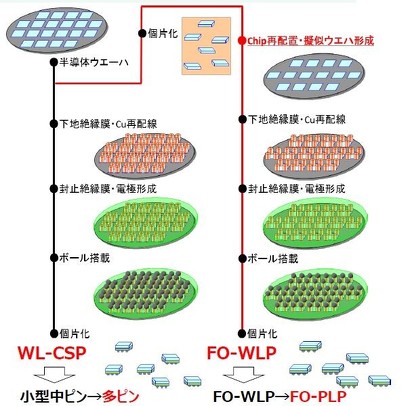

WL-CSPとFO-WLPの基本的な違い

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

本コラムの前々回から、第3章「電子デバイスパッケージ」の第3節(3.3)「各種パッケージ技術動向」を紹介し始めた。前回からは、第3章第3節第2項(3.3.2)「ウェハレベルパッケージ(WLP)、パネルレベルパッケージ(PLP)、部品内蔵基板」の説明を始めている。

「3.3.2 ウェハレベルパッケージ(WLP)、パネルレベルパッケージ(PLP)、部品内蔵基板」は以下の2つの項目によって構成される。「3.3.2.1 WL-CSP(Wafer Level-Chip Size Package)」と「3.3.2.2 FO-WLP(Fan-Out Wafer Level Package)、FO-PLP(Fan-Out Panel Level Package)、部品内蔵基板」である。その中で前回は、「3.3.2.1 WL-CSP」の概要を説明した。今回からは「3.3.2.2 FO-WLP、FO-PLP、部品内蔵基板」の概要をご紹介する。

FO-WLPと前回で説明したWL-CSPはいずれも「ウエハーレベル」と称するものの、製造工程には基本的な違いがある。WL-CSPは、回路を形成済みのシリコンウエハーをそのままパッケージ基板として使う。

これに対してFO-WLPは、回路を形成済みのシリコンウエハーを裏面から所望の厚さになるまで研削し、次いで個々のシリコンダイに切り離す(個片化)。それから「キャリア」と呼ぶウエハー(円形の板)あるいはパネル(四角い板)にシリコンダイを再配置する。この段階からパッケージングの工程が始まる。キャリアを利用してシリコンダイをまとめて樹脂モールドし、「疑似ウエハー」と呼ぶシリコンウエハーよりも大きな基板を作る。この基板に再配線層や入出力端子を形成する。

WL-CSP(左)とFO-WLP(右)の組み立て工程(ウエハーあるいは疑似ウエハーを斜め上から見た状態)[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

WL-CSP(左)とFO-WLP(右)の組み立て工程(ウエハーあるいは疑似ウエハーを斜め上から見た状態)[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)「ウエハー」ではなく、「ウエハーレベル」と呼称しているのは、ウエハーに相当する大きさのキャリアと疑似ウエハーを含んでいるから、とも言える。なおキャリアが四角いパネルであれば、「パネルレベル」のパッケージングとなる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増