300GHz帯フェーズドアレイ送信機、全CMOSで開発:100Gbps超の送信レートを実証

東京工業大学と日本電信電話(NTT)の研究グループは、300GHz帯フェーズドアレイ送信機について、アンテナや電力増幅器を含め全てCMOS集積回路で実現することに成功した。6G(第6世代移動通信)で期待される100Gビット/秒超の送信レートを実証した。

4系統の送信回路を3.8×2.6mmの1チップに集積

東京工業大学工学院電気電子系の岡田健一教授らと日本電信電話(NTT)の研究グループは2024年2月、300GHz帯フェーズドアレイ送信機について、アンテナや電力増幅器を含め全てCMOS集積回路で実現することに成功したと発表した。6G(第6世代移動通信)で期待される100Gビット/秒超の送信レートを実証した。

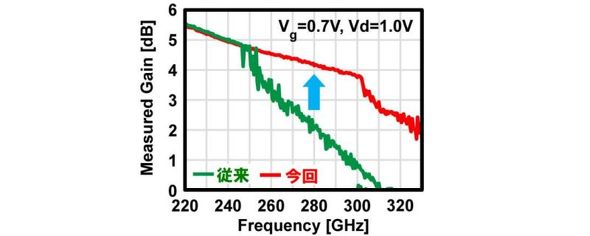

新たに開発した300GHz帯フェーズドアレイ送信機は、65nmのシリコンCMOSプロセスを用いて設計した。300GHz帯で動作する電力増幅器をCMOSで実現するため、トランジスタの配置を最適化した。この結果、寄生抵抗/容量を低減させることができ、250G〜300GHz帯での利得が従来に比べて大きく向上したという。

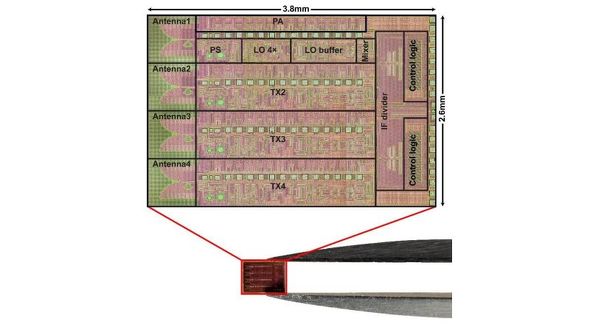

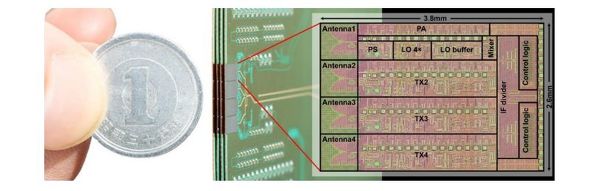

開発したトランジスタを用い増幅器を開発した。この増幅器は237〜267GHzで20dB以上の利得が得られ、飽和出力電力は251GHzで−3.4dBmを達成した。雑音指数を測定したところ、15dBが得られた。送信機ICは、オンチップのアンテナを直接駆動する増幅器が、最終段となる「増幅器ラスト」の構成とした。また、サブハーモニックミキサーや移相器、4逓倍器付きのLO回路の構成を工夫することで、面積を従来の5分の1に小型化。4系統の送信回路を3.8×2.6mmというチップサイズに集積した。

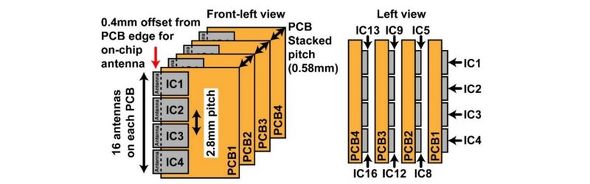

研究グループは、65nmシリコンCMOSプロセスを用いて300GHz帯送信機ICチップを作製した。アンテナ部については、イオンを照射することで基板を高抵抗化し、損失を低減している。プリント基板上に4系統の送信回路を有するCMOS ICチップを4個実装し、16アレイのフェーズドアレイ送信機を作製した。

この基板を4枚重ねて張り合わせて、16×4の2次元フェーズトアレイ送信機を作製した。ICチップの厚みは50μmとし、基板共振の影響を最小限に抑えた。さらにアンテナ部は、基板表面から0.4mm突き出すように実装。これによって、オンチップアンテナから放射される信号が反射することで生じる影響を抑えた。

研究グループは、開発した送信機の性能評価を行った。オンチップアンテナを除いた1系統の送信回路について、送信レートを高周波プローブで測定した。これにより、16QAM変調時に108Gビット/秒、32QAM変調時に95Gビット/秒となり、100Gビット/秒を超える送信レートになることを確認した。また、50cmの距離で4系統の送信回路によるアンテナビームパターンは、120°の角度掃引で設計値とほぼ一致するなど、フェーズドアレイ動作が可能であることが分かった。

なお今回の研究成果は2024年2月18〜22日に米国サンフランシスコで開催中の「ISSCC 2024(国際固体素子回路会議)」で、その詳細を発表する。

関連記事

1つのGPU/CPUで推論可能な超軽量LLM「tsuzumi」を24年3月から提供へ

1つのGPU/CPUで推論可能な超軽量LLM「tsuzumi」を24年3月から提供へ

NTTが、独自開発した大規模言語モデル(LLM)「tsuzumi」を2024年3月から提供開始する。tsuzumiは、パラメーターサイズが6億または70億と軽量でありながら、世界トップクラスの日本語処理性能を持つLLMだ。 生成AIの台頭で高まる「光電融合技術」への期待、NTTが意気込みを語る

生成AIの台頭で高まる「光電融合技術」への期待、NTTが意気込みを語る

半導体関連技術の総合展示会「SEMICON Japan 2023」にて、「日本半導体産業の発展に向けて 半導体を取り巻く先端開発」と題した講演が行われた。本稿ではその中から、NTTイノベーティブデバイス 本社 代表取締役副社長の富澤将人氏、経済産業省 商務情報政策局 情報産業課長の金指壽氏の講演内容を紹介する。 マカロン型デバイスで深部体温を計測、熱中症やうつ病の予防に

マカロン型デバイスで深部体温を計測、熱中症やうつ病の予防に

NTTは2023年11月14〜17日、「NTT R&D FORUM 2023―IOWN ACCELERATION」を開催し、貼るだけで深部体温を計測できる生体リズムモニター技術や、非侵襲で血糖トレンドを計測するデバイスなど、同社の研究開発の最新成果を展示した。 東京工大らが「超分子液晶」を作製 新たな電子デバイスの開発に期待

東京工大らが「超分子液晶」を作製 新たな電子デバイスの開発に期待

東京工業大学と大阪公立大学は、棒状の有機π電子系分子にアミド結合を導入することで、非水素結合性の「超分子液晶」を作製することに成功した。開発した超分子液晶を大面積に塗布する技術も開発した。 磁気抵抗メモリの高性能化に向けた新原理を発見

磁気抵抗メモリの高性能化に向けた新原理を発見

東京工業大学は、非磁性体の「TaSi2」において、フェルミレベル近傍にバンドの縮退点(ベリー位相のモノポール)を配置することにより、高温下でスピンホール効果を増大させる新原理を発見した。SOT(スピン軌道トルク)方式を用いる磁気抵抗メモリについて、高温下での性能改善が期待される。 光アイソレーターの回路面積、従来の1/10以下に

光アイソレーターの回路面積、従来の1/10以下に

東京工業大学らによる共同研究チームは、光アイソレーターの回路面積を従来の10分の1以下にできる技術を開発した。磁気光学結晶を1μm以下まで薄膜化して中空に保持されたシール構造に加工する技術と、シリコン光回路上の任意領域へ高精度に貼り付ける転写技術を開発し、それを適用することで実現した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す