適切なはんだ量の設定方法とスルーホールリフロー:福田昭のデバイス通信(458) 2022年度版実装技術ロードマップ(82)(1/2 ページ)

今回は、「4.1.3.4 実装」の後半2つの項目である「適切なはんだ量の設定」と「スルーホールリフロー(THR)対応コンデンサ」について解説する。

適切な量のはんだペーストを印刷することが不良を減らす

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

第448回からは、第4章「電子部品」の概要説明を始めた。前回は、4番目の項目である「4.1.3.4 実装」の概要前半をご報告した。「4.1.3.4 実装」はリフローはんだ付けに関する、「(1)チップ立ち」と「(2)適切なはんだ量の設定」「(3)スルーホールリフロー(THR)対応コンデンサ」の3つの項目で構成される。前回は「(1)チップ立ち」の概略を説明した。今回は「(2)適切なはんだ量の設定」と、「(3)スルーホールリフロー(THR)対応コンデンサ」の概要をご報告する。

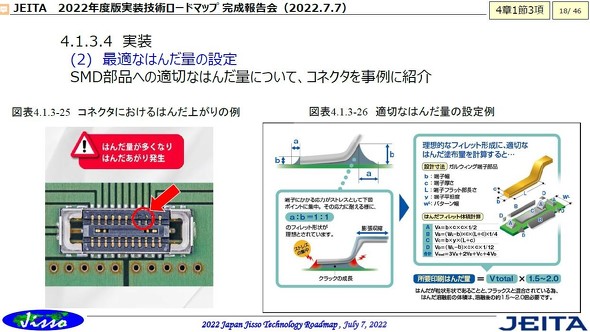

コネクタにおけるはんだ付け不良と適切なはんだ量の設定例

前回でも述べたように、「チップ立ち」を含めたリフローはんだ付け不良を防ぐには、はんだペーストの印刷量を最適化する必要がある。

例えばコネクタの場合、印刷したはんだペーストの量が過剰だと、リード間にはんだブリッジが発生したり、コネクタのコンタクト部分にはんだが上昇してくる「はんだ上がり」が起こったりする。逆にはんだ量が少ないと、コネクタの接続強度が不足する恐れがある。

最適なはんだ量の設定事例。左はコネクタにおける「はんだ上がり」の発生例。右は適切なはんだ量の設定例[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

最適なはんだ量の設定事例。左はコネクタにおける「はんだ上がり」の発生例。右は適切なはんだ量の設定例[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)はんだペーストの適切な印刷量は諸条件によって変わる。またノウハウに属する部分も存在する。一言でまとめることは難しい。適切なはんだ量の算出方法には例えば、はんだフィレットの理想的な形状から、寸法測定によってはんだの体積を求める方法がある。ただしはんだペーストにはフラックスが含まれているので、実際にはフィレットの体積よりも多くのはんだペースト(フィレット体積の1.5倍〜2.0倍とされる)を印刷しておく必要がある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼