光半導体をシリコン基板上に高速実装、東レが開発:データセンター内の光通信に適用

東レは、InP(インジウムリン)などをベースとした光半導体をシリコン基板上に実装するための材料とプロセス技術を、東レエンジニアリング(TRENG)と連携して開発した。2025年までに量産技術を確立し、早期実用化を目指す。

転写材料、キャッチ材料、実装プロセス技術を新たに開発

東レは2024年10月23日、InP(インジウムリン)などをベースとした光半導体をシリコン基板上に実装するための材料とプロセス技術を、東レエンジニアリング(TRENG)と連携して開発したと発表した。2025年までに量産技術を確立し、早期実用化を目指す。

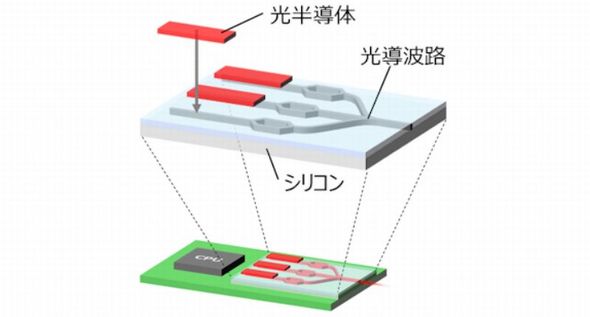

シリコンフォトニクス技術によりシリコン基板上に光回路を形成した半導体デバイスは、エネルギー損失が少ないため、長距離通信などに用いられてきた。今回は、この技術を1m未満という比較的距離が短いデータセンター内の通信に適用するため、新たな材料やプロセス技術の開発に取り組んできた。

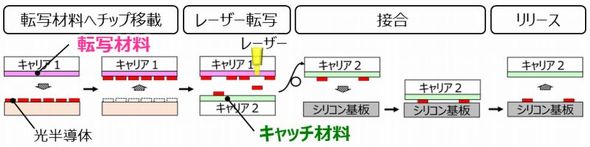

そこで今回、InPなどの光半導体をレーザーで高速転写するための「転写材料」、転写されたチップをキャッチしてシリコン基板上に直接接合できる「キャッチ材料」および、その「実装プロセス技術」を開発した。

東レはこれまで、マイクロLED向けの転写材料を開発してきた。ただ、今回用いるInPベースの光半導体は縦横の寸法が640×90μmで、一般的なマイクロLEDに比べ大きいものの、厚みは3μmと極めて薄い。このため、破損させずに一回のレーザー照射で転写できる転写材料を新たに開発した。

キャッチ材料は、これまで蓄積してきた耐熱性高分子の設計技術と粘着性の制御技術を活用。転写されたチップをキャッチしてそのままシリコン基板上に直接接合して、その後容易にリリースできる材料を新規に開発した。

さらに、レーザー転写からシリコン基板上への直接接合に至る一連のプロセス技術をTRENGと連携して開発した。実証実験により、位置精度は±2μm以内、回転ずれは±1度以内であることを確認した。実装速度は毎分6000個と極めて高速である。

関連記事

アドバンテストと東レエンジが製造関連技術で提携

アドバンテストと東レエンジが製造関連技術で提携

アドバンテストと東レエンジニアリングは、ミニ/マイクロLEDディスプレイの製造分野で、戦略的パートナーシップを締結した。製造工程で必要となる検査や転写、実装および、データ解析といった技術を組み合わせ、ディスプレイメーカーに提供していく。 ハイブリッドボンディング対応の新たな絶縁樹脂材料を開発、東レ

ハイブリッドボンディング対応の新たな絶縁樹脂材料を開発、東レ

東レは、ハイブリッドボンディング(微細接合)に対応した絶縁樹脂材料を新たに開発した。今後、材料認定を受け2028年にも量産を始める予定。半導体高密度実装における収率と信頼性向上を目指す。 次世代電池用イオン伝導ポリマー膜、東レが開発

次世代電池用イオン伝導ポリマー膜、東レが開発

東レは、イオン伝導度をこれまでの10倍に高めた次世代電池用イオン伝導ポリマー膜を開発した。金属リチウムを負極に用いた全固体電池や空気電池などの実用化に弾みをつける。 横浜国大ら、新たな半導体チップ集積技術を開発

横浜国大ら、新たな半導体チップ集積技術を開発

横浜国立大学は、新たな半導体チップ集積技術を、ディスコおよび、東レエンジニアリングと共同で開発したと発表した。開発した仮接合技術を300mmウエハー上で検証し、加工時間や材料損失が削減できることを実証した。 東レ、MLCC離型用ポリエステルフィルムを増産

東レ、MLCC離型用ポリエステルフィルムを増産

東レは、MLCC離型用のポリエステルフィルム「ルミラー」について、生産能力を増強すると発表した。岐阜工場(岐阜県神戸町)の生産設備を改造し、生産能力を現在の1.6倍に増やす。2025年に稼働予定。 東レ、空気電池用イオン伝導ポリマー膜を開発

東レ、空気電池用イオン伝導ポリマー膜を開発

東レは、リチウム空気電池のセパレーターに向けた「イオン伝導ポリマー膜」を開発した。開発したポリマー膜を適用することで、リチウム空気電池の安全性向上と長寿命化を可能にする。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に