横浜国大ら、新たな半導体チップ集積技術を開発:D2Wハイブリッド接合を可能に

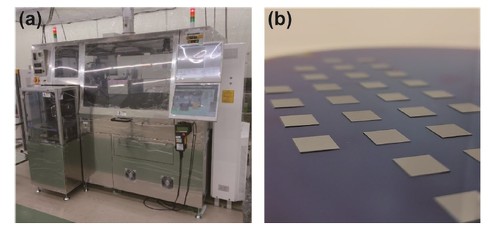

横浜国立大学は、新たな半導体チップ集積技術を、ディスコおよび、東レエンジニアリングと共同で開発したと発表した。開発した仮接合技術を300mmウエハー上で検証し、加工時間や材料損失が削減できることを実証した。

仮接合により、加工時間や材料損失を削減

横浜国立大学工学研究院の井上史大准教授は2023年5月、新たな半導体チップ集積技術を、ディスコおよび、東レエンジニアリングと共同で開発したと発表した。開発した仮接合技術を300mmウエハー上で検証し、加工時間や材料損失が削減できることを実証した。

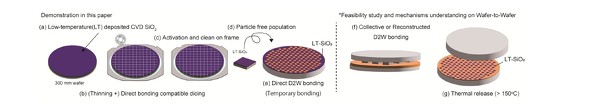

研究グループは今回、新たに開発したCVD絶縁膜を用い、ウエハー上にチップを仮接続する方法を示した。仮接続は、プラズマ活性化ダイレクトボンディングで行う。このため、仮接合界面はほとんどの前工程プロセスと互換性があるという。

界面層は薄い個体であり、ボンディング中に発生する「ダイのずれ」などを軽減できるとする。これによって、「ダイツーウエハー(D2W)」のハイブリッド接合を可能にした。仮接合で重要となるのは、低温で堆積されたSiO2膜による意図的なボイドの形成と制御された接合エネルギーだという。

そこで研究グループは、「表面粗さ」や「膜組成」「機械的特性」および、「プラズマ活性化の影響」などについて調べた。また、そのメカニズムを解明するため、無水雰囲気でのボンディングエネルギー測定や界面空孔検査、TEM分析といった界面解析を行った。

低温で堆積したSiO2は、多くのオープンスペースと水を含んでいる。これが水の貯蔵層として機能し、ポストボンドアニール中に放出される可能性があると見ている。これにより、極めて小さい力でウエハーとチップを簡単に熱剥離できることが分かった。

関連記事

AIと心電センサーで手術中の医師の感情を可視化

AIと心電センサーで手術中の医師の感情を可視化

横浜国立大学とミルウスは2023年3月31日、心電図センサーとAIを用い、手術中の医師の感情変化を可視化するシステムを開発したと発表した。熟練医師の感情を分析することで、研修医教育に役立つと期待される。 5Gマルチセクターアンテナ屋内基地局装置を開発

5Gマルチセクターアンテナ屋内基地局装置を開発

横浜国立大学とNTTドコモ、日本電業工作および富士通は、マルチセクターアンテナを実装した5Gマルチセクターアンテナ屋内基地局装置を共同開発し、28GHz帯の電波を用いた通信の実証実験に成功した。従来装置に比べ回路規模を約10分の1に小型化している。 3Dプリンタで「3次元フレキシブル配線」を作製

3Dプリンタで「3次元フレキシブル配線」を作製

横浜国立大学は、独自開発の光硬化性樹脂と、高精細な3Dプリント技術である光造形法を用い、柔軟性と導電性を有する「3次元フレキシブル配線」の作製に成功した。試作した3次元構造体の導電性は、これまで報告されていた数値に比べ100倍以上だという。 東京理科大ら、2000℃以上の高熱に耐える材料開発

東京理科大ら、2000℃以上の高熱に耐える材料開発

東京理科大学や横浜国立大学、物質・材料研究機構(NIMS)らによる研究グループは、2000℃以上という極めて高い温度に耐えられる、ジルコニウム(Zr)−チタン(Ti)合金ベースの「炭素繊維強化超高温セラミックス複合材料(C/UHTCMC)」を開発した。 シリコンフォトニクス技術で周波数人工次元を観測

シリコンフォトニクス技術で周波数人工次元を観測

横浜国立大学と東北大学、慶應義塾大学および、東京大学らの研究グループは、光集積プラットフォーム「シリコンフォトニクス」技術を用いて、「周波数人工次元」と呼ばれるトポロジカルフォトニクス関連の光学現象を観察することに成功した。 次世代半導体実装技術、「JOINT2」が現状の成果を展示

次世代半導体実装技術、「JOINT2」が現状の成果を展示

次世代半導体パッケージ実装技術の開発を目指すコンソーシアム「JOINT2」は「SEMICON Japan 2022」(会期:2022年12月14〜16日、会場:東京ビッグサイト)で、取り組みの内容や研究開発の進捗を紹介した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング