ラティスが次世代小型FPGA「Nexus 2」発表:空白だった回路規模をカバー(1/2 ページ)

ラティスセミコンダクターは、新たな小型FPGAプラットフォームとして「Lattice Nexus 2」を発表した。その第1弾として汎用FPGA「Lattice Certus-N2」のサンプル出荷を始めた。同時に、ミッドレンジFPGAプラットフォーム「Lattice Avant」の新製品として「Avant 30」と「Avant 50」なども発表した。

最新のコネクティビティやトップレベルのセキュリティをサポート

ラティスセミコンダクターは2024年12月、新たな小型FPGAプラットフォームとして「Lattice Nexus 2」を発表した。その第1弾として汎用FPGA「Lattice Certus-N2」のサンプル出荷を始めた。同時に、ミッドレンジFPGAプラットフォーム「Lattice Avant」の新製品として「Avant 30」と「Avant 50」なども発表した。

同社はこれまで、「Lattice Nexus」 やLattice Avantと呼ぶ2つのFPGAプラットフォームをベースに、パッケージや消費電力が小さく、比較的小規模から中規模レベルのFPGA製品を供給してきた。

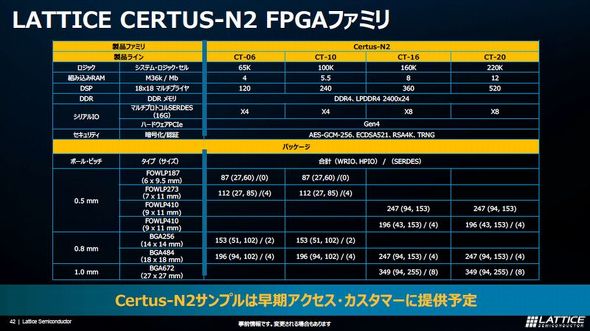

新たに投入する次世代のLattice Nexus 2は、搭載するシステムロジックセル数が65k〜220kである。既存のLattice Avantは300k〜600k、Lattice Nexusは最大100kで、これまで空白となっていた回路規模の領域をLattice Nexus 2でカバーしていくという。

Lattice Nexus 2は、TSMCの16nm FinFETプロセス技術を適用した。これまでのLattice Nexusは、Samsungの28nmFD-SOIプロセス技術を採用していたが、搭載する回路規模などに対応するため、新しいプロセス技術に切り替えたという。

Lattice Nexus 2は、最新のコネクティビティや業界トップレベルのセキュリティをサポートし、消費電力と性能の最適化などを図った。例えば、マルチプロトコル16G SERDESとPCIe Gen 4コントローラ、高速LPDDR4メモリインタフェースのサポートを始め、最大7.98Gビット/秒のMIPI D&C-PHYを搭載した。また、256ビットAES-GCMとSHA3-512による高度なセキュリティを実現。FIPS 140-3レベル2規格にも準拠し、物理的な改ざんを防止する。

性能や電力効率も向上させた。一例だが、同等クラスの競合製品に比べ、消費電力を最大3分の1に抑えた。また、エッジセンサーのモニタリングにおける電力消費は、最大10分の1で済むという。この背景にはコンフィグレーションが競合製品に比べ最大10倍も速いことが挙げられる。チップを起動する時間が18ミリ秒と極めて速いため、間欠動作が容易となる。

この他、MIPI速度が競合製品より最大で3倍速く、画像データも高速に転送ができる。さらに、パッケージサイズも競合製品に比べ最大5分の1と小さい。

Lattice Nexus 2の第1弾として今回は、汎用タイプのLattice Certus-N2を発表した。引き続き「ビデオ・コネクティビティFPGA」や「制御/セキュアFPGA」を投入していく計画である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増