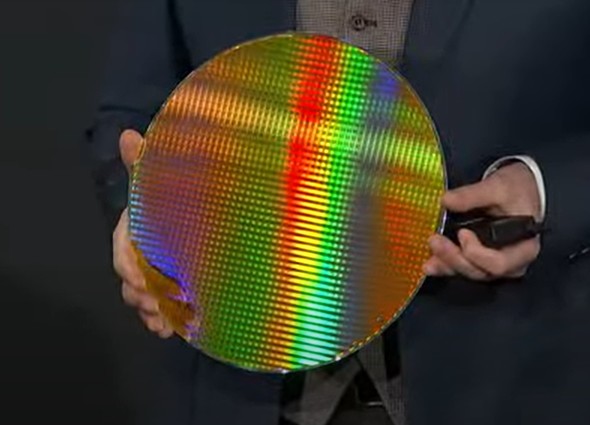

3Dフラッシュメモリ第10世代は332層で密度59%向上、キオクシアら:4.8Gb/秒と高速、低消費電力化も(1/2 ページ)

キオクシアとSandiskは、4.8Gb/秒のNANDインタフェース速度やさらなる低消費電力化などを実現する3次元(3D)フラッシュメモリ技術を開発した。この技術を導入する第10世代品は、積層数332層で、平面方向の高密度化によってビット密度は59%向上するという。

キオクシアとSandiskは、4.8Gb/秒のNANDインタフェース速度やさらなる低消費電力化などを実現する3次元(3D)フラッシュメモリ技術を開発した。この技術を導入する第10世代品は積層数332層で、平面方向の高密度化によってビット密度は59%向上するという。

速度は第8世代から33%向上

2025年2月19日(米国時間)、米国サンフランシスコで開催された半導体関連の世界最大規模の国際学会「ISSCC 2025」において発表した。両社はISSCC 2025において「A 1Tb 3b/cell 3D-Flash Memory with a 29%-Improved-Energy-Efficiency Read Operation and 4.8Gb/s Power-Isolated Low-Tapped-Termination IOs」と題して講演している。

今回発表した新しい3Dフラッシュメモリ技術は、CBA(CMOS directly Bonded to Array)技術とともに、最新のToggle DDR6.0インタフェースを新たに導入し、新たなコマンドアドレス入力手法である「SCA(Separate Command Address)プロトコル」や、さらなる消費電力の低減に有効な「PI-LTT(Power Isolated Low-Tapped Termination)技術」を活用している。

これらの高速化技術によって現在量産中の第8世代品と比較し、NANDインタフェース速度が33%の向上となる4.8Gb/秒を実現。さらに、データ入出力の電力効率を入力時に10%、出力時に34%それぞれ改善し、低消費電力と高性能を両立しているという。

SCAはCommand/Address入力用のバスとデータ転送用のバスを完全に異なるバスに分けて並列で使うことで、データ入出力の時間が短くなる技術。PI-LTTはNANDインタフェース用の電源として、既存の1.2Vの電源に加え、より低い電圧の電源も活用し、データ入出力時の電力を低減する技術だ。

第10世代は332層で、ビット密度29Gb/mm2に

両社は、これらの技術を導入する第10世代品では積層数を332層に増やし、フロアプランの最適化による平面方向の高密度化によって、ビット密度が59%向上すると説明している。プレスリリース上で数値の明記はないが、第8世代品のメモリ密度の公表値は18.3Gb/mm2のため、その59%増は29Gb/mm2となる。

CBA技術は、メモリセルの制御を担うCMOS回路とメモリセルアレイを別々のウエハーで作り込み、その2枚のウエハーを張り合わせる技術。両社が競合に先駆けて第8世代品に導入した。同技術では、CMOS回路用ウエハーとメモリセル用ウエハーをそれぞれ最適なプロセスで製造できるため、CMOS回路とメモリセルの性能を最大限に引き出せる。さらに、平面方向での高密度化も可能とし、コスト面でも利点がある。2025年2月にキオクシアホールディングスが開催した決算説明会においても同社副社長の渡辺友治氏がCBA技術について触れ、性能面のメリットの他、「(平面方向での高密度化によって)、積層を積み上げるより、安いコストでメモリ容量を上げることができる。それによって必要な製造設備の投資も抑制できる」などと紹介していた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」