次世代メモリ実用化に道筋、SOT-MRAMの書き込み電力を大幅削減:従来比で35%の削減に成功

東北大学は、高速データ書き込み性能など、スピン軌道トルク磁気記憶メモリ(SOT-MRAM)が有する特長を維持しながら、書き込み電力を従来に比べ35%削減することに成功した。

Canted角度などをシミュレーション技術で最適化

東北大学国際集積エレクトロニクス研究開発センター(CIES)の遠藤哲郎センター長らによるグループは2025年5月、高速データ書き込み性能など、スピン軌道トルク磁気記憶メモリ(SOT-MRAM)が有する特長を維持しながら、書き込み電力を従来に比べ35%削減することに成功したと発表した。

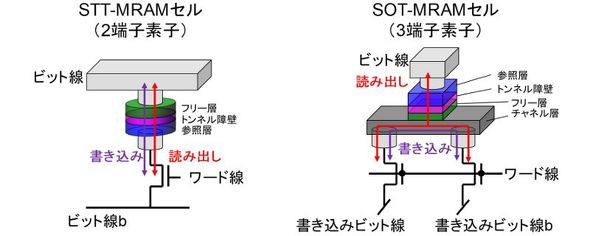

磁気記憶による不揮発性半導体メモリ(MRAM)は、AIの利用拡大などによって生じるコンピュータのエネルギー消費を抑える技術の1つとして注目されている。これまで、スピン移行トルク磁化反転型MRAM(STT-MRAM)などが実用化されてきた。ただ、将来に向けてSTT-MRAMは、さらなる高速動作への対応が課題となっていた。

東北大学の大野英男教授と深見俊輔教授らによる研究グループはこれまで、高速領域での動作に優れたスピン軌道トルク(SOT)磁化反転作用を利用したSOTメモリ素子を開発してきた。ところが、当初のSOTメモリ素子は、「耐熱性が低くCMOSと集積化できない」「熱安定性が悪く、10年間のデータ保持ができない」といった課題があった。

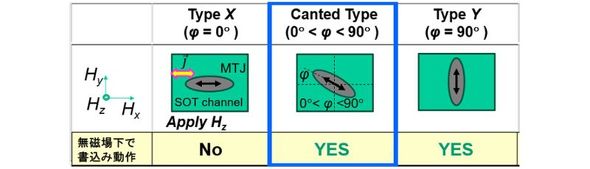

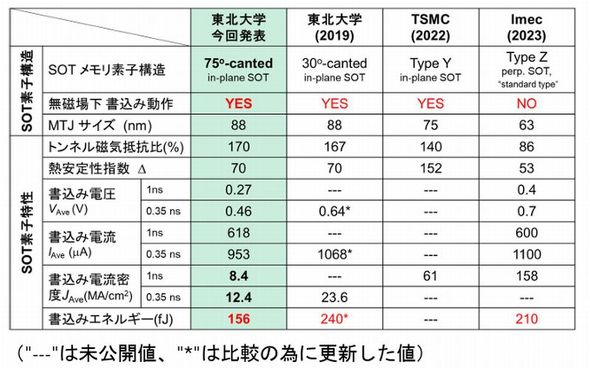

このためCIESは、400℃の耐熱性を備えた材料プロセスの開発と熱安定性に優れたSOTメモリの開発に乗り出した。具体的には、2019年に55nm世代のCMOS技術を融合させたSOT-MRAM技術を開発。Canted構造のSOTメモリ素子では、10年間データ保存できる熱安定性と、0.35ナノ秒という高速書き込み動作に成功した。2020年には、このCanted構造SOTメモリ素子を用いてSOT-MRAMチップを試作、デュアルポート動作に成功していた。一方で、「書き込み動作時の消費電力が大きい」という課題があった。

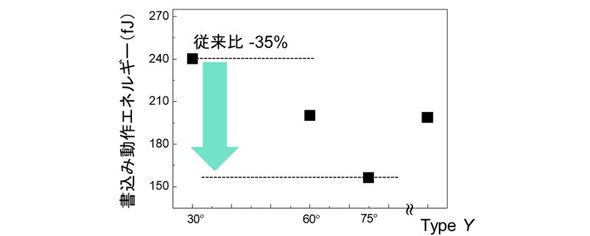

そこで今回は、300mmウエハーを用いたCMOS集積回路技術を用い、これまでの性能を保ちながら、書き込み動作時の消費電力を低減するSOTメモリ素子の開発に取り組んだ。SOTメモリ素子に搭載する磁気トンネル接合(MTJ)の積層構造で制御する結晶磁気異方性と、楕円形状MTJの傾斜角度(Canted角度)については、デバイスシミュレーションを行い、最適な書き込み電力効率となる条件を求めた。

シミュレーションの結果の基づき、これまで開発してきたSOT-MRAM技術を用いてSOTメモリ素子を試作、その特性を評価した。この結果、MTJ積層構造の最適化とCanted角度を75度にすることで、10年データ保持特性(熱安定性E/kBT=70)と、外部磁場のない環境下で0.35ナノ秒というデータ書き込み性能を維持しつつ、書き込み動作の消費電力を156フェムトジュールに抑えることができた。この値は従来に比べ35%の削減になるという。

関連記事

強磁場で超伝導ダイオード効果を示す素子を開発

強磁場で超伝導ダイオード効果を示す素子を開発

大阪大学と東北大学の共同研究グループは、鉄系超伝導体であるセレン化・テルル化鉄「Fe(Se,Te)」を用いた薄膜素子を作製し、1〜15テスラという強い磁場中で、「超伝導ダイオード効果」を観測した。 CO2とシリコン廃棄物がSiCに「生まれ変わる」 合成技術開発へ

CO2とシリコン廃棄物がSiCに「生まれ変わる」 合成技術開発へ

東北大学の研究チームと住友商事は、CO2とシリコン廃棄物を有効活用して再資源化する「カーボンリサイクル型SiC(炭化ケイ素)合成技術」の共同開発を始めた。研究期間は2028年3月までの約3年間で、「CO2削減」「産業廃棄物の有効利用」「低コスト化」の同時達成を目標とする。 半導体デバイスの発熱を制御するメカニズムを発見

半導体デバイスの発熱を制御するメカニズムを発見

東北大学と北海道大学、高輝度光科学研究センターの共同研究チームは、絶縁膜において熱の流れを自在に制御できるメカニズムを発見した。しかも、基板の種類によって膜の構造や振動特性が変化し、熱伝導が大きく変化することを確認した。 強磁場下で奇妙な電気伝導特性示す ビスマスアンチモン合金

強磁場下で奇妙な電気伝導特性示す ビスマスアンチモン合金

東京大学物性研究所は、東京都立大学や東京理科大学、神戸大学、東北大学と共同で、BiSb(ビスマスアンチモン)合金が強磁場下において、奇妙な電気伝導特性を示す状態になることを確認した。 熱電材料として「Mg2Sn単結晶」が実用レベルに

熱電材料として「Mg2Sn単結晶」が実用レベルに

東北大学と精華大学(中国)の研究グループは、マグネシウム・錫化合物(Mg2Sn)単結晶について、n型とp型の両方で熱電性能を高めることに成功した。自動車排熱や産業排熱を利用して発電する熱電発電デバイスへの応用が期待される。 東北大、太陽電池用SnS薄膜の最適組成を解明

東北大、太陽電池用SnS薄膜の最適組成を解明

東北大学は、太陽電池に用いられる硫化スズ(SnS)薄膜の組成を精密に制御する手法を開発するとともに、「組成のずれ」が電気的特性や膜質に与える影響を実験的に解明した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増