SiFiveの新RISC-VコアはAI特化 メモリ管理の革新で性能向上:エッジからデータセンターまで(2/3 ページ)

メモリ管理の革新で性能向上のボトルネックを解消

SiFiveは性能のボトルネック解消に直接関わるメモリアーキテクチャにおいて、2つの重要な新技術を導入している。それは「メモリレイテンシ耐性(Memory Latency Tolerance)」と「メモリサブシステムの高効率化(More Efficient Memory Subsystem)」だ。

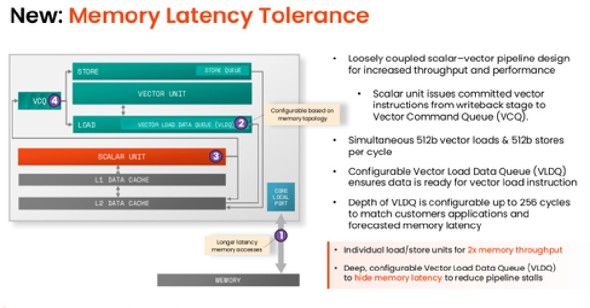

Simpson氏は特に、ロードレイテンシを隠すという洗練された設計であるメモリレイテンシ耐性に誇りを持っているという。同氏は「あらゆる命令を処理するスカラーユニットは、コミットされたベクトル命令をVector Command Queue(VCQ)にディスパッチする。ここで重要なのは、ベクトルロードが発生した場合、そのアドレスがVCQに配置されると同時に、メモリシステム(L2またはそれ以降)に送信されることだ」と説明する。

初期ディスパッチが実行から切り離されることで、メモリ応答が戻り、コンフィギュラブルなVector Load Data Queue(VLDQ)に再オーダーできるようになる。Simpson氏は「その目的は、ロードが、VLDQからデータをピックアップすることだ」と述べる。

これによって、ロード命令が最終的にVCQからポップアウトした時点で確実にデータが準備され、「1サイクルで使用できるベクトルロード」が実現する。Simpson氏は、この競争優位性を強調し、「『Hot Chips 2025』(米国カリフォルニア州パロアルト、2025年8月24〜27日)で発表されたIntelの「Xeon」新製品は、128件の未処理リクエストを処理できる。これがXeonの最上位モデルだ。われわれは現在、4コアで1024件を処理できる。この非常に素晴らしい技術によってパイプラインの停止を効率的に防ぎ、継続的な処理が可能になる」と述べている。

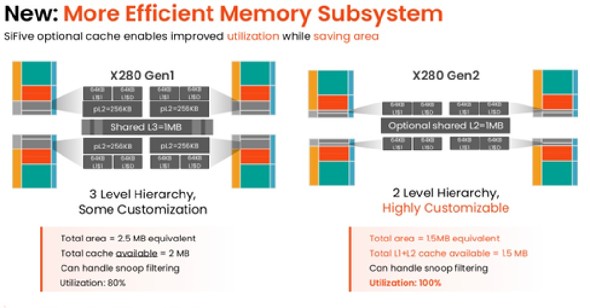

メモリサブシステムの高効率化は、キャッシュ階層をインクルーシブからノンインクルーシブへと移行させるという、もう1つの大きなアップグレードを実現している。Simpson氏は、旧世代のインクルーシブキャッシュシステムについて詳細を説明し、「共有L3キャッシュのデータは、プライベートL2/L1キャッシュで複製されるので、計2.5Mバイト相当のエリア全体のうち、有効活用できているのは40%にとどまっていた」と述べる。

第2世代設計では、こうした複製が排除されている。同氏は「現在では、データはどこにも複製されていない。1.5Mバイト相当のエリアを100%活用できている」と説明する。

「これは第1世代と比べて容量は1.5倍に、面積は60%になることを意味し、大幅な効率化とシンプルな成果を実現したといえる」(Simpson氏)

またSiFiveは、メモリの他にも、新たにハードウェアパイプライン化された指数関数ユニットを統合している。AIワークロードでは積和演算(MAC)が主流だが、次の主要なボトルネックとなりつつあるのは指数関数だ。例えば、行列エンジンで加速された大規模言語モデル「BERT」では、指数関数を含むソフトマックス関数(softmax)が残りのサイクル全体の50%超を占めている。

SiFiveのソフトウェア最適化によって、指数関数の実行時間は22サイクルから15サイクルに短縮されたが、新しいハードウェアユニットではそれを1サイクルにまで劇的に削減し、関数全体の実行時間を5サイクルにまで短縮した。この「非線形高速化の組み込み」は、あらゆるAIモデルのアクセラレーションを最大化する上で非常に重要だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増