デプレッション型r-GeO2 MOSFETの動作を実証、Patentix:エンハンスメント型実現に向けた基礎に

Patentixは、ルチル型二酸化ゲルマニウム(r-GeO2)を用いて作製したデプレッション型(ノーマリオン)MOSFETの動作実証に成功した。この成果を基に今後は、p型r-GeO2の作製技術を確立していくとともに、エンハンスメント型(ノーマリオフ)MOSFETの開発に取り組む計画である。

p型r-GeO2の作製技術確立やエンハンスメント型MOSFET実現へ

Patentixは2026年3月、ルチル型二酸化ゲルマニウム(r-GeO2)を用いて作製したデプレッション型(ノーマリオン)MOSFETの動作実証に成功したと発表した。この成果を基に今後は、p型r-GeO2の作製技術を確立していくとともに、エンハンスメント型(ノーマリオフ)MOSFETの開発に取り組む計画である。

Patentixはこれまで、n型不純物であるSb(アンチモン)を添加したn型r-GeO2の成膜/導電性制御技術を確立し、n+層成膜によるオーミックコンタクトの実現や、n-層成膜によるショットキーバリアダイオード(SBD)の動作実証に成功してきた。

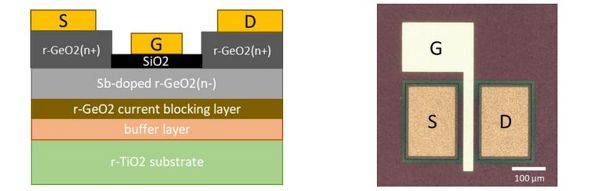

今回は、これまで開発した成膜技術をベースに、n型r-GeO2のみで作製できるデプレッション型MOSFETを試作し、トランジスタの動作検証を行った。作製したr-GeO2 MOSFETは、r-TiO2基板上に不純物を添加したr-GeO2膜で電流遮断層を形成。その上部に厚みが160nmのSbドープn-チャネル層と、ソース/ドレインn+層を形成した。ゲート酸化膜には膜厚が75nmのSiO2を、電極にはPt/Tiをそれぞれ用いた。

このデバイス構造では、負のゲート電圧を加えるとゲート絶縁膜直下から空乏層を伸ばし、ドレイン−ソース間の電流経路を遮断して電源をオフにすることができる。

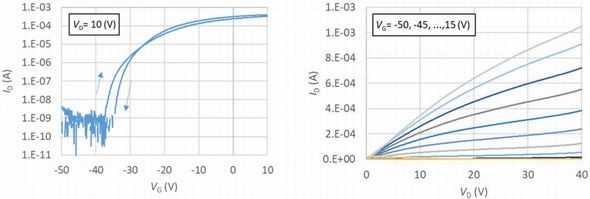

作製したr-GeO2 MOSFETの特性を評価した。この結果、ゲート電圧(VG)によりドレイン電流(ID)が5桁以上のオン/オフ比で変化。負のゲート電圧でドレイン電流がオフするデプレッション型トランジスタとしての動作を確認した。また、ID−VD特性のデータから、ドレイン電圧の増加に伴い線形から飽和特性へ移行するのが確認できた。

関連記事

「世界初」FZ法でルチル型二酸化ゲルマニウムバルク結晶を育成、Patentix

「世界初」FZ法でルチル型二酸化ゲルマニウムバルク結晶を育成、Patentix

Patentixは、FZ法(浮遊帯域溶解法)を用いて、ルチル型二酸化ゲルマニウム(r-GeO2)バルク結晶を育成することに成功した。引き続き、結晶のさらなる大型化と高品質化に取り組み、ハーフインチサイズのr-GeO2バルク基板について早期実現を目指す。 二酸化ゲルマニウム半導体技術が前進、イオン注入でn型導電性

二酸化ゲルマニウム半導体技術が前進、イオン注入でn型導電性

Patentixは、次世代のパワー半導体材料として注目されているルチル型二酸化ゲルマニウム(r-GeO2)結晶膜に対し、イオン注入法によりドナー不純物を添加することで、n型導電性を付与することに成功した。これにより、複雑な構造を有するパワー半導体デバイスの作製が容易になる。 ルチル型二酸化ゲルマニウムのバルク結晶を合成

ルチル型二酸化ゲルマニウムのバルク結晶を合成

Patentixは、次世代のパワー半導体材料として注目されている「ルチル型二酸化ゲルマニウム(r-GeO2)」のバルク結晶を合成することに成功した。今後はこのバルク結晶を種結晶として用い、引き上げ法などによって大口径化や高品質化を図り、市場投入を目指す。 三拍子そろった好材料 次なるパワー半導体「二酸化ゲルマニウム」の可能性

三拍子そろった好材料 次なるパワー半導体「二酸化ゲルマニウム」の可能性

SiCやGaNのさらに次の世代のパワー半導体材料として期待される二酸化ゲルマニウム。その社会実装を目指す立命館大学発のスタートアップ、Patentixで社長兼CEOを務める衣斐豊祐氏と、Co-CTO(共同最高技術責任者)を務める金子健太郎氏に話を聞いた。 ルチル型GeO2で「世界初」半導体デバイスの動作確認

ルチル型GeO2で「世界初」半導体デバイスの動作確認

Patentixは、r-GeO2(ルチル型二酸化ゲルマニウム)単結晶薄膜上にショットキーバリアダイオード(SBD)を形成し、その動作を確認した。 ルチル型酸化物半導体でデバイス動作を確認

ルチル型酸化物半導体でデバイス動作を確認

立命館大学と京都大学、物質・材料研究機構の研究チームは、xを0.53付近に調整したルチル型(r-)GexSn1-xO2薄膜を、r-TiO2基板上に格子整合(格子整合エピタキシー)させることで、薄膜内の貫通転位密度を極めて小さくすることに成功した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点