「メビウスの輪」で位相ジッターを削減、マイクレルが新シンセサイザICを発売:アナログ設計

マイクレル・セミコンダクターは、位相ジッターが小さいPLLシンセサイザIC「ClockWorksファミリー」のサンプル出荷を開始した。例えば、156.25MHz出力の品種では、位相ジッターのrms値が標準58fs(オフセット周波数が1.875M〜20MHzのとき)である。

「位相ジッターが100fsを切るほど小さいPLLシンセサイザICの製品化は業界初。パッケージの寸法が同等の競合他社品に比べて、位相ジッターは1/4程度だ」(同社の広帯域マーケティング担当ディレクターのRami Kanama氏、図1)。これまでのPLLシンセサイザICと同等の価格帯ながら、SAW発振器に匹敵するほど位相ジッターが小さいという。

このほか、ClockWorksファミリーは、電源電圧の変動に対する耐性が高く、消費電力が小さいことも特徴である。対象機器は、サーバやストレージ、ネットワーク機器、放送機器など。

ループ状の伝送線路で発振回路を形成

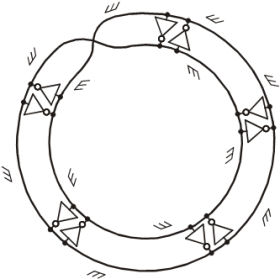

位相ジッターを従来に比べて大幅に削減できた理由は、「Rotary Traveling Wave Oscillator(RTWO)」と呼ぶ新たな発振回路を採用したことにある(図2)。

RTWOとは、差動伝送線路をループ状に形成し、ループのつなぎ目を「メビウスの輪」のように半ひねりしたもの。伝送線路によって形成されるインダクタンスと、線路間に形成されるキャパシタンスによって、発振周波数が決まるのだという。ループのつなぎ目を半ひねりするのは、伝送線路の高周波信号の位相を180度回転させ、発振させるためだと説明した。

図2 「Rotary Traveling Wave Oscillator(RTWO)」技術のイメージ図

図2 「Rotary Traveling Wave Oscillator(RTWO)」技術のイメージ図差動伝送線路をループ状に形成し、ループのつなぎ目を「メビウスの輪」のように半ひねりすることで発振回路を形成する。出典:マイクレル・セミコンダクター

一般的には、インバータを複数直列に並べてリングオシレータを形成し、発振回路を形成する。ただ、各インターバータがランダム雑音を生み出すため、位相ジッターを抑えにくいことや、電源電圧の変動に特性が影響されやすい、リーク電流が大きいといった課題があったという。RTWO技術を採用すれば、このような課題の解決が図れる。製造には一般的なCMOS製造プロセスが使え、コストを押し上げる要因にはならない。

RTWO技術は、もともとアナログICやミクスドシグナルICを手掛けるファブレス企業であるMultigigが開発したものだった。マイクレルは、Multigigと協業し、RTWO技術を採用したPLLシンセサイザICを製品化することを、2009年9月に発表していた。

入力は、水晶発振器が生成した25MHzの基準信号。内蔵PLL回路で周波数を高めて出力する。出力周波数は、最大850MHz。出力形式は、LVCMOSまたは、LVPECL、LVDS、HCSLである。出力の系統数は、差動形式のとき最大8系統、シングルエンド形式のとき最大16系統である。OTP(One Time Programmable)メモリを搭載しており製品出荷時に出力周波数を決められる「SM802xxx」と、出力周波数が固定の「SM84xxx」がある。SM802xxxの単価は、1000個購入時に5.10米ドルである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

図1 マイクレル・セミコンダクターの広帯域マーケティング担当ディレクターのRami Kanama氏

図1 マイクレル・セミコンダクターの広帯域マーケティング担当ディレクターのRami Kanama氏