第27回 n型MOSFETにp型追加して利得向上:Analog ABC(アナログ技術基礎講座)(2/2 ページ)

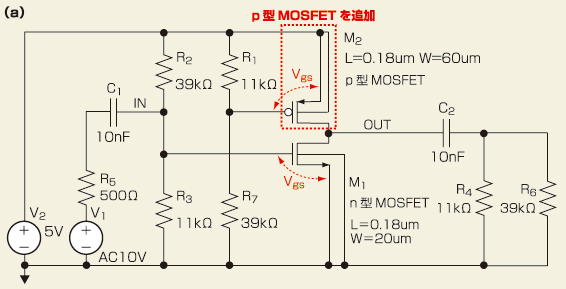

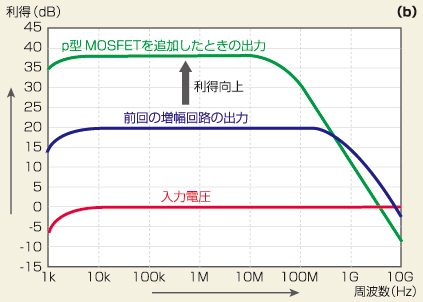

図2(a)は、本連載の第26回に紹介した増幅回路に、能動負荷としてp型MOSFETを追加した回路です。p型MOSFETのVgsを、n型MOSFETのVgsと同じにするために、R1を11kΩ、R7を39kΩに設定しました。図2(b)は、p型MOSFETを追加した増幅回路の小信号特性です。利得は前回の20dBより大幅に高くなり、38dBとなりました。一方で、利得を高められたのと引き替えに、高域遮断周波数は、800MHzから40MHzに下がっています。

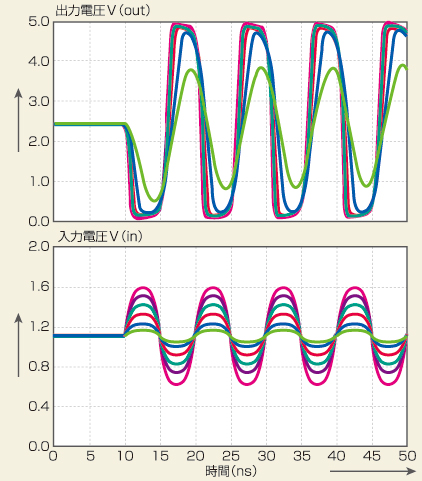

続いて、過渡解析に移ります(図3)。入力信号には、周波数が100MHzの正弦波を使いました。0.1Vppと0.2Vpp、0.4Vpp、0.6Vpp、0.8Vpp、1.0Vppと振幅を大きくした正弦波信号を入力しています。

振幅が0.1Vと小さい場合、位相の遅れが顕著です。これは小信号特性の高域遮断周波数(およそ40MHz)よりも変化の早い100MHzを入力したためです。また、100MHzの利得は30dBに低下していますので、出力振幅も電源レベルまで達していません。入力信号の周波数を10MHzに下げたところ、出力信号の位相が遅れることも無く、電源レベルまで十分な振幅を得られることを確認しました。

特性のずれが特性劣化を引き起こす

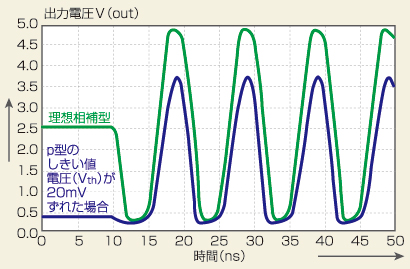

今まで使ってきた増幅回路のp型MOSFETは、理想的な相補型でした。従って、出力動作点は電源電圧の1/2に相当する2.5Vになっています(図4)。しかし実際には、理想的な相補型トランジスタは作れません。

例えば、図4に示したように、p型のしきい値電圧(Vth)が20mV大きくなり、n型のVthが0.7V、p型のVthが0.72Vとなっただけで、動作点がずれてしまいます。結果、出力波形のデューティ比もずれ、小信号特性の利得も低下してしまいます。

今回、負荷抵抗に能動素子を使うことで、利得を高めることができました。特にCMOS増幅回路は、相補型デバイス間の特性の差異が小さいので、能動素子を使う利点は大きいと言えます。

しかし、利得を高められる替わりに、応答速度が遅くなる点や、しきい値(Vth)のわずかなずれが、利得や動作点に大きな影響を与える点が、欠点に挙げられます。次回は、欠点を改善する手法を紹介していきたいと思います。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- デンソー、ロームに対する株式取得提案を正式表明

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 次世代パワー半導体 「期待の5材料」の現在地――電子版2026年3月号

- ソニー・ホンダモビリティ、EV「AFEELA」開発中止

図2(a) 能動負荷としてp型MOSFETを追加 p型MOSFETを追加した回路図です。

図2(a) 能動負荷としてp型MOSFETを追加 p型MOSFETを追加した回路図です。 図2(b) 能動負荷としてp型MOSFETを追加 周波数特性です。赤色の線は入力電圧を示しています。

図2(b) 能動負荷としてp型MOSFETを追加 周波数特性です。赤色の線は入力電圧を示しています。 図3 入力電圧と出力電圧の振幅波形の変化 周波数が100MHzと高いとき、振幅が小さくなると位相の遅れが顕著になります。また、利得が下がってしまい、出力振幅も電源レベルまで達していません。

図3 入力電圧と出力電圧の振幅波形の変化 周波数が100MHzと高いとき、振幅が小さくなると位相の遅れが顕著になります。また、利得が下がってしまい、出力振幅も電源レベルまで達していません。 図4 相補型デバイスの特性のずれが特性劣化を引き起こす p型MOSFETのしきい値電圧(Vth)が20mVずれたときの出力電圧の波形。

図4 相補型デバイスの特性のずれが特性劣化を引き起こす p型MOSFETのしきい値電圧(Vth)が20mVずれたときの出力電圧の波形。