「このデモは世界初」、ザイリンクスが次期FPGAの28Gbps波形を披露:ET2011 高速シリアルインタフェース技術

ET2011でザイリンクスは、最先端FPGAに搭載する高速シリアルトランシーバの動作を実演した。これまでに公開していたデモの構成から、最終的な製品の形態に近づけた構成で28Gビット/秒の高速データ伝送波形を披露した。

ザイリンクスは、2011年11月16〜18日に開催された「Embedded Technology 2011/組込み総合技術展(ET2011)」(会場はパシフィコ横浜)で、28nm世代の半導体プロセスで製造する次期ハイエンドFPGA「Virtex-7」に搭載する28Gビット/秒対応の高速シリアルトランシーバ(SERDES:シリアライザ/デシリアライザ)の動作を実演した。

同社はVirtex-7ファミリで、単一のパッケージに複数のFPGAチップ(ダイ)や高速SERDESダイを混在させて納める独自技術「スタックド シリコン インターコネクト」を適用することを発表している(参考記事)。今回のデモはそのVirtex-7ファミリの中でも最も広い入出力帯域幅を備える「Virtex-7 HT」を想定しており、同品種で採用するパッケージの内部に、スタックド シリコン インターコネクトを使って28Gビット/秒動作のSERDESダイを実装して、そのデータ伝送波形を見せた。

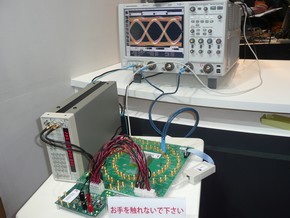

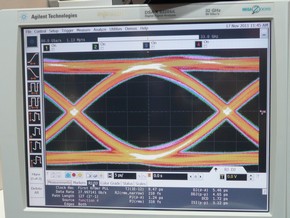

左側の写真は、デモの全景である。Virtex-7に搭載する高速SERDESを28Gビット/秒で動作させ、データ伝送波形をサンプリングオシロスコープで観測して見せた。右側の写真は、サンプリングスオシロコープの画面である。ジッターの各種パラメータの測定値も読み取れる。(クリックで拡大)

左側の写真は、デモの全景である。Virtex-7に搭載する高速SERDESを28Gビット/秒で動作させ、データ伝送波形をサンプリングオシロスコープで観測して見せた。右側の写真は、サンプリングスオシロコープの画面である。ジッターの各種パラメータの測定値も読み取れる。(クリックで拡大)同社はこれまでに、内部基板に樹脂材料を使う旧来型のパッケージを使って、その内部の樹脂基板上に直接28ビット/秒の高速SERDESダイを実装した構成では同様のデモを見せていたが、スタックド シリコン インターコネクトの特徴であるSi(シリコン)材料を使った支持基板(インターポーザ)上に同ダイを搭載した構成での実演は今回が世界初だという。

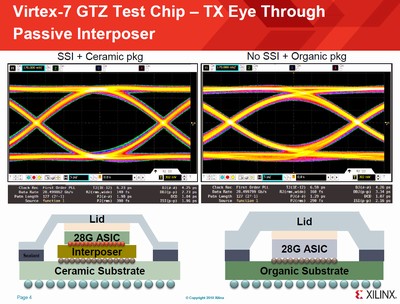

デモの横で見せていたプレゼンテーションスライド。左側は今回のデモ、右側は従来のデモで用いていたパッケージ内の構成である。今回のデモでは、パッケージの底部の基板(Substrate)と28Gビット/秒SERDESの間に、シリコンインターポーザが挿入された。それにもかかわらず、データ伝送波形の品質は従来の構成と同等以上を維持している。「スタックド シリコン インターコネクトを導入しても、シグナルインテグリティが低下しないことを示す結果だ」(XilinxのSystem IO Specialist FAEであるOusama Hage氏)と説明した。出典:ザイリンクス(クリックで拡大)

デモの横で見せていたプレゼンテーションスライド。左側は今回のデモ、右側は従来のデモで用いていたパッケージ内の構成である。今回のデモでは、パッケージの底部の基板(Substrate)と28Gビット/秒SERDESの間に、シリコンインターポーザが挿入された。それにもかかわらず、データ伝送波形の品質は従来の構成と同等以上を維持している。「スタックド シリコン インターコネクトを導入しても、シグナルインテグリティが低下しないことを示す結果だ」(XilinxのSystem IO Specialist FAEであるOusama Hage氏)と説明した。出典:ザイリンクス(クリックで拡大)このVirtex-7 HTの28Gビット/秒SERDESは、OIF(Optical Internetworking Forum)が定める電気インタフェースの共通仕様「CEI-28G」の「VSR(Very Short Reach)」に準拠するという。今回のデモ構成でPRBS 31の疑似ランダムパターンで評価したところ、ビット誤り率は10e−12以下に抑えられていたと説明した。消費電力については、28Gビット/秒動作時にチャネル当たり200mW程度だという。

なおザイリンクスは、今回のデモで使ったパッケージの内部に28Gビット/秒SERDESダイの他にFPGAダイが納められているかどうかについては、明言を避けた。仮にFPGAダイが内蔵されていないとすれば、Virtex-7 HTの最終的な製品の形態でFPGAダイが同時動作した場合、SERDESの波形品質は今回のデモに比べて悪化する懸念がある。これに対してザイリンクスは、「スタックド シリコン インターコネクトでは、単一のパッケージ内にFPGAダイとSERDESダイを封入しながらも、両者を電気的に絶縁することが可能だ。同時動作時にSERDESダイが受けるノイズの影響を低く抑えられる」と説明した。

10Gビット/秒の“エラーフリー”や28nm世代品の評価ボード群もアピール

この他ザイリンクスは、「Virtex-7 485T」のエンジニアリングサンプル品を使って、この品種に搭載する10.4Gビット/秒のSERDESのデモも見せた。このSERDESが出力した高速シリアルデータの信号を、バックプレーンの模擬基板を経由させて同じSERDESの受信回路に戻してビット誤り率を測定し、その値が極めて低いこともアピールしていた。

送信側と受信側の伝送距離は1m程度で、その間の損失は約30dB、模擬基板の材質は「Nelco N4000-13」である。PRBS 31の疑似ランダムパターンでビット誤り率は10e−12〜10e−14に抑えられており、エラービットの検出数はゼロだった。

さらにザイリンクスのブースでは、パートナー企業である東京エレクトロン デバイスが、28nm世代のFPGAの評価ボード群を展示していた。

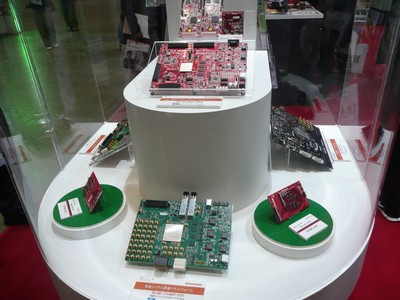

東京エレクトロン デバイスが展示した評価ボード群。最上段に展示した赤色のボードはザイリンクスが28nm世代で提供する製品群のうち、価格対性能比に最適化した「Kintex-7」の評価ボードである。2012年の初旬に出荷できるように準備しているという。下段の中央には、ハイエンド品「Virtex-7」の評価ボードも展示した。「エンジニアリングサンプル品を載せた評価ボードで、高速SERDESの動作速度の上限が6.6Gビット/秒にとどまっている。ザイリンクスからの製品版の出荷状況に応じて、評価ボードも用意する」(東京エレクトロン デバイスの説明員)という。(クリックで拡大)

東京エレクトロン デバイスが展示した評価ボード群。最上段に展示した赤色のボードはザイリンクスが28nm世代で提供する製品群のうち、価格対性能比に最適化した「Kintex-7」の評価ボードである。2012年の初旬に出荷できるように準備しているという。下段の中央には、ハイエンド品「Virtex-7」の評価ボードも展示した。「エンジニアリングサンプル品を載せた評価ボードで、高速SERDESの動作速度の上限が6.6Gビット/秒にとどまっている。ザイリンクスからの製品版の出荷状況に応じて、評価ボードも用意する」(東京エレクトロン デバイスの説明員)という。(クリックで拡大)関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増