東芝とSanDiskが128GビットNANDフラッシュを開発、サイズは1セントコイン以下:ISSCC 2012

東芝とSanDiskは、容量が128GビットのNANDフラッシュメモリチップを開発した。3ビット/セル技術と19nmプロセスを用いて製造しており、チップサイズは1セントコインよりも小さい。

東芝とSanDiskは、1個のメモリセルに3ビットのデータを記憶できる3ビット/セル技術と19nmプロセスを用いて、容量が128GビットのNANDフラッシュメモリチップを共同で開発し、その技術的な詳細を半導体集積回路技術の国際会議「ISSCC(International Solid-State Circuits Conference)2012」(2012年2月19〜23日、米国カリフォルニア州サンフランシスコ)において発表した。チップの面積は170.6mm2。すなわち容量密度は0.75Gビット/mm2である。この技術は既に量産品に適用されており、2012年2月から製品出荷を始めている。

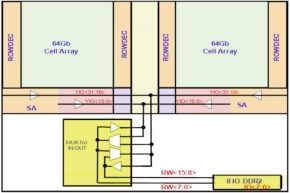

今回開発したNANDフラッシュメモリチップは、64Gビットの容量を持つ2つのプレーンで構成されている。各プレーンは、両サイドに行デコーダ回路を集積している。プレーンの下側には、SanDisk独自のメモリアレイ構成「ABL(All Bit Line)」に対応したセンスアンプ回路が組み込まれている。従来はプレーンの両側に分けて配置していたセンスアンプ回路を片側にまとめたことや、チャージポンプ回路を見直したことにより、メモリセル以外の周辺回路の面積を約20%削減した。

また、独自開発の高速書き込みアルゴリズムとメモリセル間の干渉を抑えるエアギャップ構造を採用することで、18Mバイト/秒と高いデータ書き込み速度を実現した。これは、3ビット/セル技術を適用したNANDフラッシュメモリチップとして最も高い書き込み速度だという。なお、この高速書き込みアルゴリズムとは、3段階に分けて行うメモリセルへのデータ書き込みについて、2段階目で全てのビットを大まかに書き終えた後、3段階目で微修正するというものだ。これにより、微細化によって増大する浮遊ゲート間の干渉による影響を約5%に抑えることができる。さらに、QDBM(Quad-Data-Bus Multiplex)と呼ぶデータ転送アーキテクチャによって、トグルモードでのデータ転送速度で400Mビット/秒を達成した。

この他、高速書き込み時に起こる温度上昇による影響を抑えるために、デジタル温度センサーと温度補償回路をチップ内に搭載している。

その他の主な仕様は以下の通り。ページサイズは16Kバイトで、ECC(エラー符号訂正)に対応した。電源電圧は2.7〜3.6V(入出力電圧は1.8V)である。

関連記事

指先にテラビットが載る、IntelとMicronが20nm世代のNANDフラッシュ量産

指先にテラビットが載る、IntelとMicronが20nm世代のNANDフラッシュ量産

IntelとMicron Technologyは、20nm世代の半導体プロセス技術を適用した128GビットのNAND型フラッシュメモリの量産を2012年前半に始める。20nm世代の128Gビット品の量産は、業界初になる見通しだ。マルチチップ品の記録容量は1T(テラ)ビットに達する。 SanDiskが19nm世代のNANDフラッシュをサンプル出荷へ、2ビット/セルで64Gビット

SanDiskが19nm世代のNANDフラッシュをサンプル出荷へ、2ビット/セルで64Gビット

SanDiskは19nmプロセス技術で製造するNAND型フラッシュメモリを今四半期中にサンプル出荷する。2011年の下半期には量産を始める予定だ。 Samsung Electronics、20nmクラスの製造技術を適用したNANDフラッシュの量産を開始

Samsung Electronics、20nmクラスの製造技術を適用したNANDフラッシュの量産を開始

Samsungが、20nmクラスのプロセス技術を採用したNANDフラッシュメモリの製造を開始した。来年には、10nmクラスの製造技術を用いたメモリの製造にも着手する予定だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円