Intel偺14nm僾儘僙僗偲ARM乽Cortex-A53乿傪嵦梡丄Altera偺乽Stratix 10 SoC乿丗價僕僱僗僯儏乕僗 婇嬈摦岦

Altera偼丄師悽戙SoC FPGA乽Stratix 10 SoC乿偺CPU僐傾偵丄嵟戝4僐傾偺64價僢僩僾儘僙僢僒乽ARM Cortex-A53乿傪嵦梡偡傞丅Stratix 10 SoC偼Intel偺14nm僩儔僀僎乕僩僾儘僙僗偱惢憿偝傟傞偨傔丄ARM Cortex-A53偼廬棃偺僨儏傾儖僐傾僾儘僙僢僒乽ARM Cortex-A9乿偵斾傋偰丄彮側偔偲傕6攞偺僨乕僞張棟擻椡偑摼傜傟傞偲偄偆丅

丂Altera偼2013擭10寧29擔乮暷崙帪娫乯丄師悽戙SoC乮System on Chip乯 FPGA乽Stratix 10 SoC乿偺CPU僐傾偵丄嵟戝4僐傾偺64價僢僩僾儘僙僢僒乽ARM Cortex-A53乿傪嵦梡偡傞偲敪昞偟偨丅Stratix 10 SoC偼丄Intel偺14nm僩儔僀僎乕僩僾儘僙僗偱惢憿偝傟傞偨傔丄ARM Cortex-A53偼廬棃偺僨儏傾儖僐傾僾儘僙僢僒乽ARM Cortex-A9乿偵斾傋偰丄彮側偔偲傕6攞偺僨乕僞張棟擻椡偑摼傜傟傞偲偄偆丅Stratix 10 SoC偼2014擭10寧埲崀偵僥乕僾傾僂僩偝傟傞梊掕偱偁傞丅

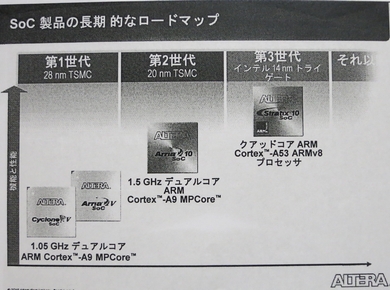

丂摨幮偼丄2013擭6寧偵乽Generation 10 FPGA仌SoC乿偺奣梫傪敪昞偟偨丅Intel偺14nm僩儔僀僎乕僩僾儘僙僗偱惢憿偝傟傞僴僀僄儞僪惢昳偺乽Stratix 10乿偲丄TSMC偺20nm僾儘僙僗傪梡偄偰惢憿偝傟傞儈僢僪儗儞僕惢昳乽Arria 10乿偱偁傞丅偦偺帪揰偱偼丄乽Arria 10 SoC乿偼摦嶌廃攇悢偑1.5GHz偺僨儏傾儖僐傾僾儘僙僢僒乽ARM Cortex-A9乿傪嵦梡偡傞偲敪昞偟偰偄偨偑丄Stratix 10 SoC偵搵嵹偡傞僾儘僙僢僒僐傾偵偮偄偰偼丄偙傟傑偱柧傜偐偵偟偰偄側偐偭偨丅

丂ARM Cortex-A53偼丄64價僢僩柦椷傪娷傓ARM v8柦椷僙僢僩傾乕僉僥僋僠儍傪儀乕僗偲偟偨僾儘僙僢僒僐傾偱丄摨偠64價僢僩僐傾偺乽ARM Cortex-A57乿偵斾傋偰彫宆丒徣揹椡僐傾偲偄偆偺偑摿挿偩丅Intel偺14nm僩儔僀僎乕僩媄弍偲慻傒崌傢偣傞偙偲偱丄廬棃偺ARM Cortex-A9傪搵嵹偟偨SoC FPGA偵斾傋偰彮側偔偲傕6攞偺僨乕僞張棟擻椡傪幚尰偱偒傞偲偄偆丅傑偨丄32價僢僩儌乕僪偱偺摦嶌傕壜擻偱丄ARM Cortex-A9傪搵嵹偟偨SoC FPGA偲偺僜僼僩僂僃傾屳姺惈傕偁傞丅偨偩丄崱夞偼ARM Cortex-A53僐傾偺摦嶌廃攇悢傗丄CPU僐傾偲儊儌儕僐傾娫偁傞偄偼IP僐傾偲愙懕偡傞僆儞僠僢僾僶僗婯奿側偳丄僠僢僾偺徻嵶偵偮偄偰偼柧傜偐偵偟側偐偭偨丅

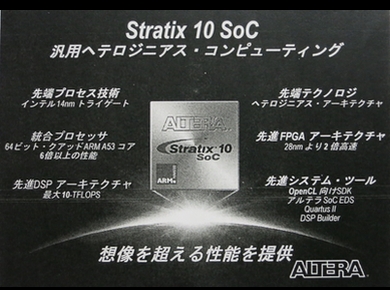

丂Stratix 10 SoC偼丄儘僕僢僋晹偺摦嶌廃攇悢傪1GHz埲忋偵偡傞偙偲偑壜擻偲側傝丄28nm僾儘僙僗偱惢憿偝傟傞Stratix V偵斾傋偰2攞偺惈擻偲側傞丅傑偨丄DSP僽儘僢僋偵偼丄僴乕僪僂僃傾壔偝傟偨晜摦彫悢揰DSP傪幚憰偡傞偙偲偱丄嵟戝10僥儔FLOPS偺墘嶼惈擻傪幚尰偡傞偙偲偑壜擻偱偁傞丅

丂Altera偱僄儞儀僨僢僪僾儘僙僢僔儞僌儅乕働僥傿儞僌扴摉偺僔僯傾僨傿儗僋僞傪柋傔傞Chris Balough巵偼丄ARM Cortex-A53傪慖戰偟偨棟桼偵偮偄偰丄乽儘僕僢僋晹傗DSP晹偺惈擻傪峫椂偟丄僿僥儘僕僯傾僗僐儞僺儏乕僥傿儞僌傪幚尰偡傞偨傔偺嵟揔側CPU僐傾傪慖傫偩丅偙傟偵傛偭偰亀崅偄墘嶼惈擻亁偲亀掅偄揹椡徚旓亁偲偄偆2偮偺栚昗傪払惉偱偒偨乿偲榖偡丅偝傜偵丄乽ARM Cortex-A53偼斈梡惈偑偁傝丄崱屻偼儈僢僪儗儞僕偺SoC FPGA偺CPU僐傾偵傕棙梡偱偒傞乿偲弎傋偨丅

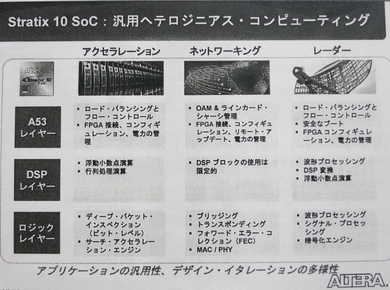

丂Balough巵偼丄Stratix 10 SoC偺僔僗僥儉墳梡偵偮偄偰丄3偮偺帠椺傪嫇偘偨丅乽僨乕僞僙儞僞乕傾僋僙儔儗乕僔儑儞乿丄乽僱僢僩儚乕僉儞僌偲僨乕僞揱憲乿偍傛傃乽儗乕僟乕乿偱偁傞丅偄偢傟傕丄僔僗僥儉偺僐儞僩儘乕儖僾儗乕儞偵幚憰偝傟偰偄傞儂僗僩僾儘僙僢僒偺墘嶼晧壸偑憹戝偡傞拞偱丄偦偺晧壸傪Stratix 10 SoC偑幚憰偝傟偨儔僀儞僇乕僪側偳偵暘攝偡傞偙偲偑偱偒傞丅偙傟偵傛偭偰丄愝旛偺搳帒旓梡傗揹椡徚旓傪梷偊偮偮丄僔僗僥儉偺張棟擻椡傪岦忋偝偣傞偙偲偑壜擻偲側傞丅

丂Altera偼丄SoC FPGA偺僜僼僩僂僃傾奐敪娐嫬傕梡堄偟偰偄傞丅暲楍張棟傪峴偆僿僥儘僕僯傾僗僐儞僺儏乕僥傿儞僌僔僗僥儉岦偗偺僾儘僌儔儈儞僌僣乕儖偲偟偰乽OpenCL岦偗僜僼僩僂僃傾奐敪僉僢僩乮SDK乯乿偑偁傞丅FPGA梡偵嵟揔壔偝傟偨僣乕儖偱OpenCL僜僼僩僂僃傾偐傜僴乕僪僂僃傾傪惗惉偡傞偙偲偑偱偒傞丅傑偨丄乽ARM DS-5 Altera Edition僣乕儖僉僢僩乿傪娷傓Altera偺乽SoC僄儞儀僨僢僪僨僓僀儞僗僀乕僩乮EDS乯乿傪梡偄傞偲丄僿僥儘僕僯傾僗峔惉偺僠僢僾慡懱偺僨僶僢僌傗壜帇壔偑壜擻偵側傞偲偄偆丅

- 傕偆僗儅儂偱傗偗偳偟側偄!? 敄偝100兪m偺抐擬僔乕僩

- 僀儞僥儖丄戝婯柾側恖堳嶍尭偐

- 夡傟偵偔偄掞峈婍丄彫偝偄僨傿僗僋儕乕僩乗乗撈帺怓懪偪弌偟丄崙撪幵嵹巗応傊怹摟傊

- 帋嶌偵摿壔偡傞捠斕戙棟揦儅僂僓乕偑擔杮偵僒億乕僩嫆揰傪奐愝

- 怴惗Broadcom偵岦偗弨旛拝乆丄堦晹帠嬈攧媝偺壜擻惈傕丠

- Industry4.0偵岦偗偨惢昳愴棯傪壛懍丄儕僼傽儗儞僗僨僓僀儞偱奐敪巟墖

- 擭岟彉楍攑偟偨乬婡摦椡偁傞1000恖懱惂乭偱挧傓怴惗僒僀僾儗僗偺崙撪愴棯

- 儐乕僽儘僢僋僗丄戝嶃偵僆僼傿僗傪奐愝

- 僗儅乕僩僌儔僗偱帇妎忈偑偄幰偺奜弌傪僒億乕僩丄尰嵼抧傪墦妘抧偱傕僔僃傾

- Apple偑AR儊乕僇乕傪攦廂丄幵嵹巗応嶲擖偵杮崢丠

娭楢婰帠

慡偰偺婡婍偵傾儖僥儔惢昳傪丄懡條側惢昳孮偱帺摦幵/嶻嬈婡婍暘栰偵挧傓

慡偰偺婡婍偵傾儖僥儔惢昳傪丄懡條側惢昳孮偱帺摦幵/嶻嬈婡婍暘栰偵挧傓

戝庤FPGA儀儞僟乕偺傾儖僥儔偼丄2013擭屻敿偐傜2014擭偵偐偗丄偝傑偞傑側怴惢昳搳擖傪梊掕偡傞丅14nm偲偄偆嵟愭抂僾儘僙僗嵦梡昳偐傜55nm僼儔僢僔儏儊儌儕撪憼偺掅僐僗僩僼傽儈儕丄偝傜偵偼揹尮IC傪傕庤妡偗傞丅庢傝埖偄惢昳偑懡條壔偟偮偮偁傞拞丄2013擭7寧偵擔杮傾儖僥儔偺幮挿偵廇擟偟偨僴儞僗丒僠儏傾儞巵偼丄乽慡偰偺惢昳偵傾儖僥儔惢昳傪搵嵹偡傞乿偲偄偆丅僠儏傾儞巵偵擔杮朄恖幮挿偲偟偰偺書晧傗帠嬈愴棯傪暦偄偨丅 僔儕僐儞僐儞僶乕僕僃儞僗傪壜擻偲偡傞傾儖僥儔SoC丄奐敪娐嫬傕惍偆

僔儕僐儞僐儞僶乕僕僃儞僗傪壜擻偲偡傞傾儖僥儔SoC丄奐敪娐嫬傕惍偆

FPGA儀乕僗偺愝寁庤朄偼丄愝寁偺廮擃惈傪妋曐偟偮偮嵟愭抂僾儘僙僗媄弍傪妶梡偱偒傞偙偲偐傜拲栚傪廤傔偰偄傞丅偙偆偟偨拞偱乽僔儕僐儞僐儞僶乕僕僃儞僗乿傪採彞偟偰偄傞傾儖僥儔偼丄嵟愭抂FPGA媄弍傪儀乕僗偲偟偨SoC愝寁傪悇恑偟偰偄傞丅 乽20nm傑偱偼TSMC丄14nm埲崀偼Intel乿丄Altera偑惢憿愴棯傪愢柧

乽20nm傑偱偼TSMC丄14nm埲崀偼Intel乿丄Altera偑惢憿愴棯傪愢柧

Altera偼師悽戙FPGA偵偮偄偰Intel偺14nm僩儔僀僎乕僩媄弍偺嵦梡傪寛傔丄Intel偵惗嶻埾戸偡傞宊栺傪掲寢偟偨丅Altera偱偼偙偺媄弍傪嵟忋埵偺FPGA惢昳偵揔梡偟丄乽偙傟傑偱偺媄弍偱偼惉偟偊側偐偭偨惈擻傗婡擻傪幚尰偟偰偄偔乿峫偊偩丅 Intel偺14nm僾儘僙僗媄弍傪梡偄偨乽Stratix 10乿傪敪昞丄擭撪偵僥僗僩僠僢僾弌壸

Intel偺14nm僾儘僙僗媄弍傪梡偄偨乽Stratix 10乿傪敪昞丄擭撪偵僥僗僩僠僢僾弌壸

傾儖僥儔偼師悽戙FPGA乽Generation 10乿偲偟偰丄Intel偺14nm僩儔僀僎乕僩僾儘僙僗偱惢憿偡傞僴僀僄儞僪惢昳乽Stratix 10乿偲丄TSMC偺20nm僾儘僙僗傪梡偄偨儈僢僪儗儞僕惢昳乽Arria 10乿傪敪昞偟偨丅Stratix 10偼丄尰峴偺Stratix V偵斾傋偰惈擻偑2攞偲側傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

Altera偺乽Stratix 10 SoC乿偺僷僢働乕僕奜娤

Altera偺乽Stratix 10 SoC乿偺僷僢働乕僕奜娤

Altera偱僄儞儀僨僢僪僾儘僙僢僔儞僌儅乕働僥傿儞僌扴摉偺僔僯傾僨傿儗僋僞傪柋傔傞Chris Balough巵

Altera偱僄儞儀僨僢僪僾儘僙僢僔儞僌儅乕働僥傿儞僌扴摉偺僔僯傾僨傿儗僋僞傪柋傔傞Chris Balough巵