ザイリンクスが20nmプロセスFPGAの提供を開始、440万ロジックのVirtexも登場:ザイリンクス UltraScale

ザイリンクスは、20nmプロセスのFPGA「UltraScale」の提供を開始する。ミッドレンジの「Kintex UltraScale」ファミリとハイエンドの「Virtex UltraScale」ファミリだ。Virtex UltraScaleファミリでは、ロジックセルを440万個搭載した品種も用意する。

ザイリンクスは2013年12月10日(米国時間)、同年7月にテープアウト(設計完了)を発表した20nmプロセスのFPGA「UltraScale」の提供を開始した。ミッドレンジの「Kintex UltraScale」とハイエンドの「Virtex UltraScale」の2つのファミリを投入する。同時に、20nmプロセスFPGAに対応した統合開発環境「Vivado Design Suite」も提供を開始する(関連記事:ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」)。

ロジックセルが440万の品種も

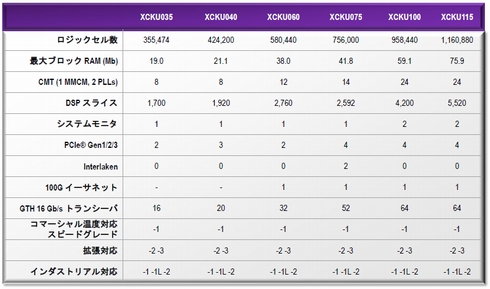

Kintex UltraScaleは、ロジックセル数が最大116万個までの6品種をそろえた。DSPスライスは最大5520。通信速度が16.3ギガビット/秒のトランシーバを最大64個搭載している。

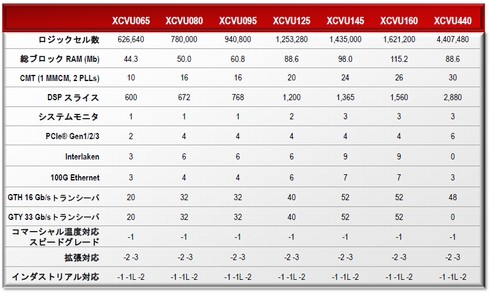

ハイエンドのVirtex UltraScaleファミリには、440万個のロジックセルを搭載した「XCVU440」を用意した。XCVU440は、同ファミリの中でロジックセルの最も大きい品種で、DSPスライスは2880個、16.3Gビット/秒のトランシーバを48個搭載している。28nm世代のプロセスを用いた「Virtex 7シリーズ」の中で最大規模品となる「Virtex-7 2000T」に比べ、ロジックセル数は2倍となっている。

さらに、Kintex UltraScale/Virtex UltraScaleは、100ギガビットイーサネットMAC(Media Access Control)と150ギガビット/秒のInterlaken IP(Intellectual Property)コアを搭載している。どちらも、28nmプロセスを採用した「Kintex 7シリーズ」「Virtex 7シリーズ」にはなかったものだ。

ザイリンクス日本法人社長のサム・ローガン氏は、UltraScaleのテープアウトを発表した際に、「FPGAを、単にロジックを入れるデバイスとしてではなく、電源回路やCPUを搭載し、SoC(System on Chip)といえるようなデバイスにした」と述べている。UltraScaleにイーサネットMACやInterlaken IPコアを追加したのも、そうした方針を引き継いでいる。「必要な周辺機能を追加することで、FPGAというよりも、SoCになっている」(同氏)。

Kintex UltraScaleとVirtex UltraScaleには、端子互換性がある。ローガン氏は、「デバイスだけで低コスト化を考えるのは難しいので、エコシステム全体でコスト削減を図る必要がある。UltraScaleではファミリ間で端子互換性を持たせて、IPと基板をリユースすることでコストを抑えられる。将来的に16nmプロセスのFPGAを出したときにも端子互換性があるようにする予定だ」と述べている。

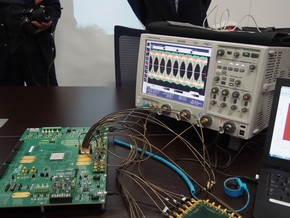

Kintex UltraScaleの1つである「XCKU040」(ロジックセル数は42万4200個)を使ったデータ送受信のデモ。右の画像のほぼ中央にある銀色のパッケージがXCKU040。16.4ギガビット/秒で通信している(クリックで拡大)

Kintex UltraScaleの1つである「XCKU040」(ロジックセル数は42万4200個)を使ったデータ送受信のデモ。右の画像のほぼ中央にある銀色のパッケージがXCKU040。16.4ギガビット/秒で通信している(クリックで拡大)関連記事

ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクスは、20nmプロセス技術を用いたFPGAのテープアウト(設計完了)を発表した。同時に、20nmプロセス採用FPGAなどに適用する新世代アーキテクチャ「UltraScale」の概要も公表した。新プロセス、新アーキテクチャを採用した製品の出荷は2013年10〜12月を予定している。 もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

大手FPGAベンダーであるXilinxは、最先端の半導体製造プロセスを用いた製品開発に意欲的なことで知られている。同社は、TSMCの20nmプロセスを用いた次世代品を、2013年10〜12月期にサンプル供給する方針を既に明らかにしている。日本法人のザイリンクスで社長を務めるサム・ローガン氏に、通信機器におけるASIC/ASSPからFPGAへの置き換えの進展や、競合のAlteraが発表したIntelの14nmプロセス採用に対する見解などについて聞いた。 「20nm世代は性能と集積度が2倍、消費電力が1/2に」、ザイリンクスが発表

「20nm世代は性能と集積度が2倍、消費電力が1/2に」、ザイリンクスが発表

FPGA大手のXilinxが、20nm世代の半導体プロセスで製造する次期FPGA「8シリーズ」の製品戦略を発表した。プロセスの微細化に加えて、28nm世代を適用する現行の「7シリーズ」で新たに導入した複数の技術基盤を改良することで、性能と集積度を2倍に高めたり、消費電力を半分に抑えたりすることが可能になるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

ザイリンクス日本法人社長のサム・ローガン氏

ザイリンクス日本法人社長のサム・ローガン氏