25Gbpsの高速光伝送を、5mW/1Gbpsの低消費電力で実現:新技術 CPU間光伝送(2/2 ページ)

» 2015年02月23日 15時30分 公開

[EE Times Japan]

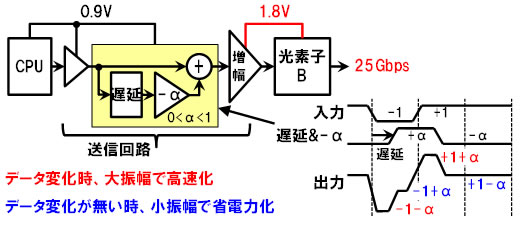

1.8Vで動作可能に

今回開発した技術では、CPUからの送信信号が−1、+1に変化するタイミングに限定して信号を増幅することで、1.8V程度の振幅を断続的に発生させている。これにより、3.3Vよりも低い1.8Vの電源電圧で動作させることが可能になった。さらに、データが変化しないところは小振幅で電力を使わないので、さらなる低消費電力化が図れる。

仕組みは次の通りだ。

- 送信データと、それを遅延させたデータを、−α(0<α<1)倍したものを足し合わせる

- これにより、送信データが−1から+1に変化する場合、+1が+1+αに増幅される

- 送信データが+1から−1に変化する場合、−1が−1−αに変化する

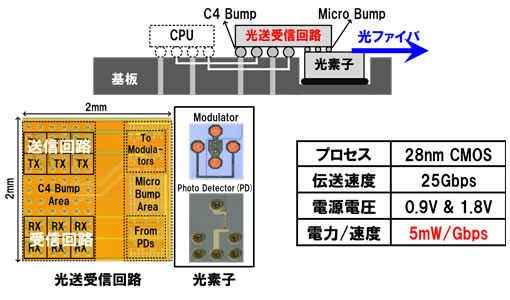

同技術により、25Gbpsの高速伝送を1Gbps当たり5mWで実現できることを確認したという。この消費電力は従来の約半分である。

富士通は、この技術をCPUや光モジュールのインタフェース部などに適用し、2018年度の実用化を目指す。また、複数の光送受信回路を並べた、毎秒テラビット級の高速伝送を実現する、サーバやスパコンの高性能化が期待できるとしている。

関連記事

CPU間データ通信速度で32Gbpsを達成、富士通研が新たな送受信回路を開発

CPU間データ通信速度で32Gbpsを達成、富士通研が新たな送受信回路を開発

富士通研究所は、CPU間のデータ通信速度を従来比で約2倍となる32ギガビット/秒(Gbps)に高速化できる送受信回路を開発した。次世代サーバ向けCPUに適用し、2014年ごろの実用化を目指す。 400Gビット級光伝送技術の実用化にめど、NTTなど3社が開発

400Gビット級光伝送技術の実用化にめど、NTTなど3社が開発

NTTとNEC、富士通の3社は、チャネル当たり毎秒400Gビット級の光伝送技術の実用化にめどをつけた。開発した技術を光送受信装置に実装すれば、既存の光ファイバを活用して、従来に比べて4倍の光伝送を実現することが可能となる。 Intelが100Gbpsの光モジュールを開発、Open Compute Summitでお披露目

Intelが100Gbpsの光モジュールを開発、Open Compute Summitでお披露目

Intelが100Gbpsのデータ転送速度を実現可能なシリコンフォトニクスベースのモジュールを発表した。そのお披露目の場となった「Open Compute Summit」では各社から、大規模なデータセンター向けのさまざまな革新的技術が発表された。 「光FPGA」の実動デモをAlteraが披露、100GbEのトラフィックを伝送

「光FPGA」の実動デモをAlteraが披露、100GbEのトラフィックを伝送

FPGA大手ベンダーのAlteraは、光インタフェースを搭載したFPGAを開発し、その動作デモを実演した。通信機器内でFPGAが入出力する高速データの伝送を、銅線を使った電気通信から光ファイバーを利用する光通信に置き換えることを狙う。ネットワークインフラの帯域幅の急拡大に対応する取り組みだ。 産総研、生きた細胞の機能を光エネルギーで操作できる技術を開発

産総研、生きた細胞の機能を光エネルギーで操作できる技術を開発

生体透過性の高い近赤外レーザーで熱と活性酸素種を発生する有機色素と、カーボンナノホーンから成る分子複合体(ナノモジュレーター)を作製。この分子複合体を用いて、生きた細胞の機能を操作できる光制御技術を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR

図3 振幅を大きくする仕組み 出典:富士通

図3 振幅を大きくする仕組み 出典:富士通 図4 開発した光送受信回路のチップ写真と、チップの特性 出典:富士通

図4 開発した光送受信回路のチップ写真と、チップの特性 出典:富士通