25Gbpsの高速光伝送を、5mW/1Gbpsの低消費電力で実現:新技術 CPU間光伝送(1/2 ページ)

富士通らは、CPU間の光伝送について、25Gbpsの高速伝送を1Gbps当たり5mWで実現する技術を開発した。従来は3V以上の電源電圧で光素子を駆動していたが、0.8Vで駆動できるようになり、低消費電力化も図れているという。

富士通、富士通研究所、Fujitsu Laboratories of America(FLA)、技術研究組合 光電子融合基盤技術研究所(PETRA)、新エネルギー・産業技術総合開発機構(NEDO)は2015年2月23日、サーバやスーパーコンピュータ(以下、スパコン)のCPU間高速データ通信を、1ギガビット/秒(Gbps)当たり5mWで実現するシリコンフォトニクス技術を用いた光送受信回路を共同開発したと発表した。同技術は、2015年2月22〜26日に米国で開催されている国際学会「ISSCC(IEEE International Solid-State Circuits Conference) 2015」で発表される。

高速化と低消費電力化はトレードオフ

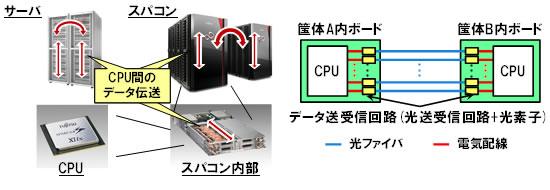

サーバやスパコンでは、高性能化に伴いCPUが搭載された筐体内や筐体間での通信データ量がますます増加している。このため、サーバやスパコンの性能を向上するには、CPU単体の演算性能だけでなく、それらをつなぐCPU間のデータ通信速度を高めることも必要となる。

次世代の高性能スパコンで期待されているシリコンフォトニクス技術を用いた光送受信技術では、光素子の実用的な伝送速度の限界が25Gbpsとなっている。そのため、光素子およびそれを駆動する電子回路の光送受信回路を複数並べ、全体として高速化を図る方法が考えられている。一方で、CPU間データ通信は4年で2倍の高速化が求められており、電力を一定にして高速化を実現するには、光送受信回路の電力を半分にする必要がある。

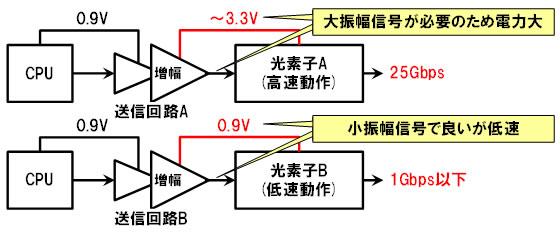

CPUなどは通常0.9Vで動作するが、一般的に、25Gbpsの高速な光送受信では3V以上の電源電圧で光素子を駆動している。光素子を駆動する送信回路も高い電源電圧で動作させ、光素子に常に振幅の大きな信号を送ることで高速動作を実現するため、低消費電力化が難しい。また、低消費電力化のために、CPUと同じ0.9Vで動作する光素子を用いると、1Gbps程度の低速動作しか実現できないという問題がある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 次世代パワー半導体 「期待の5材料」の現在地

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

図1 高性能サーバやスパコンのCPU間データ通信 出典:富士通

図1 高性能サーバやスパコンのCPU間データ通信 出典:富士通 図2 光送受信回路の課題 出典:富士通

図2 光送受信回路の課題 出典:富士通