CPU間データ通信速度で32Gbpsを達成、富士通研が新たな送受信回路を開発:ISSCC 2013(1/2 ページ)

富士通研究所は、CPU間のデータ通信速度を従来比で約2倍となる32ギガビット/秒(Gbps)に高速化できる送受信回路を開発した。次世代サーバ向けCPUに適用し、2014年ごろの実用化を目指す。

富士通研究所は2013年2月18日、半導体集積回路技術の国際会議「ISSCC(IEEE International Solid-State Circuits Conference) 2013」(2013年2月17〜21日、米カリフォルニア州サンフランシスコ)において、CPU間のデータ通信速度を従来比で約2倍となる32ギガビット/秒(Gbps)に向上できる回路技術を発表した。データ処理能力のさらなる向上が求められている次世代サーバ向けCPUに適用し、2014年以降の実用化を目指す。

なお、富士通は、サーバ向け製品である「SPARCプロセッサ」やASSP、ASICといったシステムLSI事業は、パナソニックのシステムLSI事業と統合し、マーケティング・設計・開発機能に特化した「ファブレスSoC新会社」として分離独立させる計画である。しかし、今回発表した送受信回路のような、次世代サーバ向けCPUなどに搭載する基盤技術については、富士通研究所をはじめとした富士通グループで研究開発を続ける方針だ(関連記事)。

次世代サーバのボトルネック

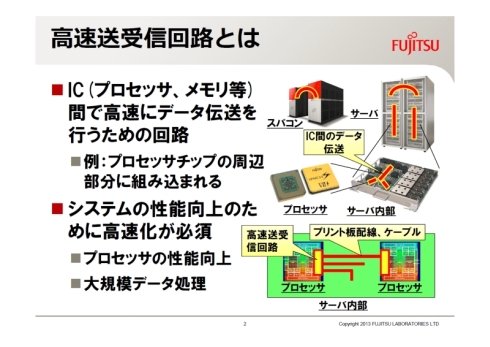

現在、CPUに搭載するプロセッサコアの性能向上と同時に、1つのCPUに多数のプロセッサコアを搭載して並列処理させるメニーコア技術の導入などにより、システムレベルのデータ処理性能は大幅に向上している。こうした中で、さらなるデータ処理性能の向上を目指すために複数のCPUを搭載するサーバのような機器の場合、CPU間におけるデータ通信速度がボトルネックとなるケースもある。

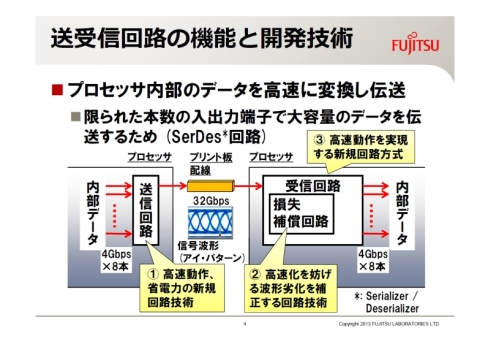

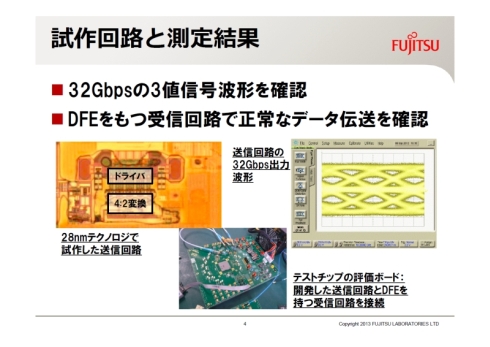

この課題を解決するために富士通研究所が開発したのが、CPU間のデータ通信速度をGbpsまで高められる回路技術である。この回路技術は、CPUからデータを送信する送信回路(ISSCC 2013発表番号2.7)、送信したデータを受信する受信回路(ISSCC 2013発表番号2.1)、伝送路における信号品質の劣化を補償するための損失補償回路(ISSCC 2013発表番号2.5)の3つから構成されている。以下に、これら3つの回路技術について説明しよう。

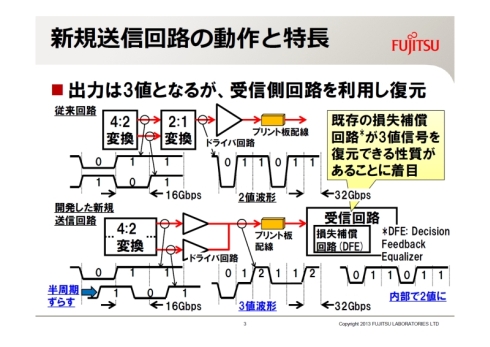

2:1変換回路が不要な送信回路

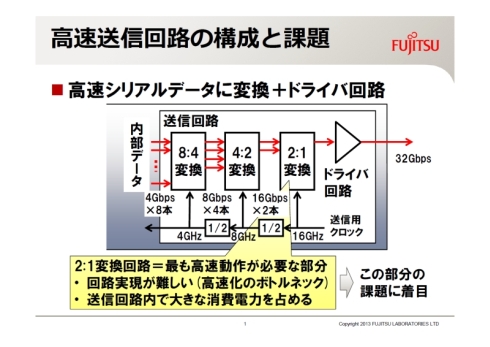

サーバ向けCPUに集積された送信回路では、プロセッサコアから多チャンネルで出力される内部データを最終的に1チャンネルまで多重化してから外部に送信するのが一般的だ。この多重化では、データ通信速度を2倍に高める一方で入力されるチャンネル数を2分の1に減らす変換回路を複数接続して、最終的に1チャンネルにする。特に、最終段に来る2:1変換回路は処理速度が最も高速になるため消費電力も大きくなる。もし、データ送信速度を32Gbpsまで高めようとすると、2:1変換回路の消費電力は極めて大きくなる上に、処理速度も素子の動作限界に達してしまうという。

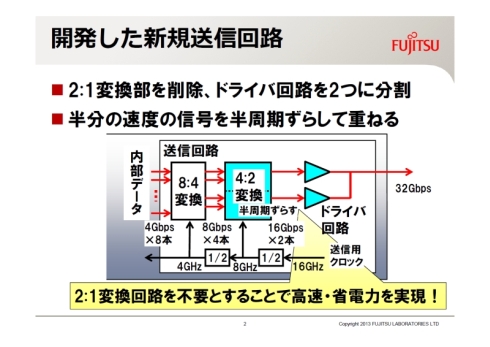

富士通研究所が新たに開発した送信回路は、この最終段の2:1変換回路を不要にした点で、従来の送信回路と大きく異なる。その分、ドライバ回路を2つに分割している。その上で、従来は2:1変換回路の前段にあった4:2変換回路から出力される信号を半周期ずらして、ドライバ回路で加算して出力する。

この結果、送信信号の出力は、従来の2値(0と1)ではなく、3値(0、1、2)の波形となる。出力が3値波形となっても、受信回路内にある損失補償回路(DFE:Decision Feedback Equalizer)が3値信号を復元する機能を元々有しているので、特別な回路を追加する必要はない。最も消費電力の大きい2:1変換回路を削除したことで、送信回路の消費電力は従来比で約30%削減された。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」