Stratix 10メカニカルサンプルを公開 アルテラ:抵抗1本で設定できる30Aデジタル電源も(1/2 ページ)

アルテラ(Altera)は「組込み総合技術展 Embedded Technology 2015」(会期:2015年11月18〜20日で、CPUコアを搭載し、14nmプロセスを搭載する2016年出荷予定のFPGA「Stratix 10 FPGA & SoC」のメカニカルサンプルを公開した。その他、開発中の30A対応デジタル電源モジュール製品も披露した。

アルテラ(Altera)は2015年11月18〜20日に開催されている展示会「組込み総合技術展 Embedded Technology 2015」(以下、ET2015)で、CPUコアを搭載し、14nmプロセスを搭載する2016年出荷予定のFPGA「Stratix 10 FPGA & SoC」(以下、Stratix 10)のメカニカルサンプル(テストチップ)を公開した。デジタル電源モジュール製品でも、ソフトウェアプログラムを不要にする機能を備えた開発中の30A対応製品も披露した。

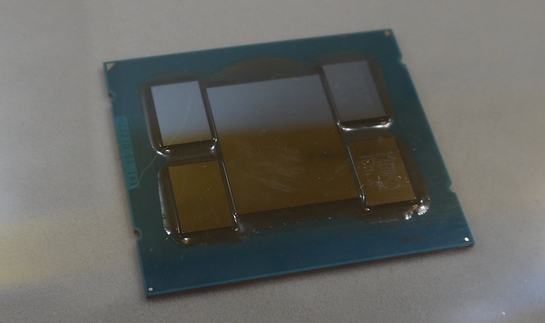

国内初公開となった「Stratix 10 FPGA & SoC」のメカニカルサンプル。中央の大きな黒いダイがインテル14nmプロセスを採用する「Core Fabric」で、その周囲のダイがトランシーバを構成した「TILE」 (クリックで拡大)

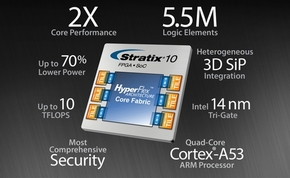

国内初公開となった「Stratix 10 FPGA & SoC」のメカニカルサンプル。中央の大きな黒いダイがインテル14nmプロセスを採用する「Core Fabric」で、その周囲のダイがトランシーバを構成した「TILE」 (クリックで拡大)メカニカルサンプルを公開したStratix 10は、アルテラが「ハイエンドSoC(System on Chip) FPGA」と位置付ける次世代FPGA。プログラマブル領域とともに、CPUコア「ARM Cortex-A53」を搭載する次世代FPGA。CPUとロジックエレメント領域を持つダイ「Core Fabric」(コア ファブリック)とは別に、トランシーバやメモリなどは「TILE」(タイル)と呼ぶダイで形成。それぞれに最適なプロセスを用いた上で、System in Package(SiP)技術で接続、1パッケージに統合する形でデバイスを構成する。Core Fabricについては、インテル(Intel)の14nm トライゲートプロセスを採用し製造。TILEについては、PCI Express Gen3などに対応するトランシーバの他、HBM(High Bandwidth Memory)2対応の積層型DRAMなどをそろえることを発表している。

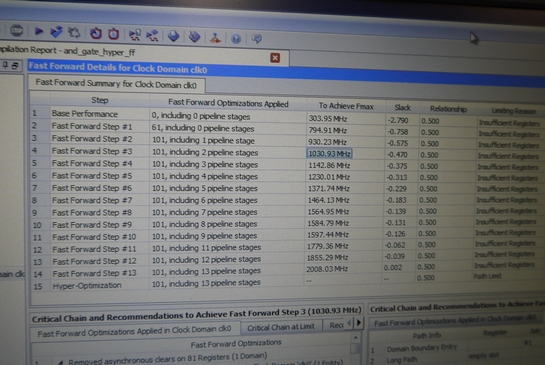

ET2015では、メカニカルサンプルとともに、Stratix 10の大きな特長である「HyperFlexアーキテクチャ」と呼ぶインタコネクト上にレジスタ(Hyper-Register)を配置できる技術を紹介した。配線上にレジスタを置くことで、昨今の微細プロセス採用FPGAで性能のボトルネックとなっている「配線遅延」を極めて小さくする。Hyper-Registerを使用することで、配線の転送速度を2倍程度、高めることが可能だ。

Stratix 10の開発ツールでの、配線速度見積もり結果画面。Hyper-Registerを使用しない場合の配線での転送速度は、303.95MHz相当だが、使用することで794.91MHz相当に高速されるとの結果が表示された。さらにパイプラインステージを設けることで、さらに高速化できることも示されている

Stratix 10の開発ツールでの、配線速度見積もり結果画面。Hyper-Registerを使用しない場合の配線での転送速度は、303.95MHz相当だが、使用することで794.91MHz相当に高速されるとの結果が表示された。さらにパイプラインステージを設けることで、さらに高速化できることも示されている「これまでユーザーからは、プロセス以外の面でのFPGAの進化を要求され続けてきた。Stratix 10は、HyperFlexアーキテクチャなどでそうした要望に応えることのできたFPGA。既にStratix 10への関心は高く、ツール提供段階だが良い評価を多数得ている」(同社)とする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増