求む、「スーパーメモリ」:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(16)(2/2 ページ)

「スーパーメモリ」の候補技術

「スーパーメモリ」の目標仕様をもう少し詳しく見ていこう。必須の要件は不揮発性メモリであること、製造プロセスがCMOSロジックと互換であること、記憶容量当たりの製造コストがDRAMに近いこと、データの読み書きを高速に実行できること、データの書き換え可能な回数が10年の使用に耐えること(具体的には10の15乗回以上)、動作時の消費電力が低いこと、高い電源電圧を必要としないこと、などである。

スーパーメモリの候補は既に存在する。1つは「スピントルク注入型磁気メモリ(STT-MRAM)」、もう1つは「抵抗変化メモリ(RRAM)」である。

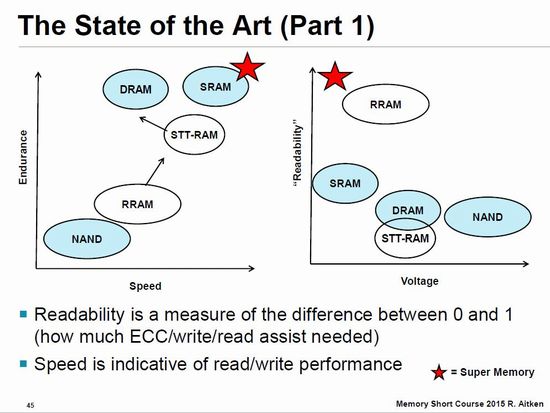

データ読み書きの高速性と書き換え可能回数のバランスで見ると、SRAMとDRAMはいずれも非常に高い位置に来ており、バランスが良い。一方でNANDフラッシュは書き換え回数の制限があり、なおかつ書き込みに時間がかかることから、低い位置にレイアウトされてしまう。

スーパーメモリの候補であるSTT-RAMは、SRAMとDRAMに近い高速性と書き換え可能回数を有する。RRAMは書き換え可能回数と速度とも、やや劣る。

またデータ読み出しの容易さ(Readability)と電源電圧のバランスでみると、RRAMが非常に良い位置につけている。STT-RAMは読み出しの容易さではかなり劣る。

最終勝者は誰か

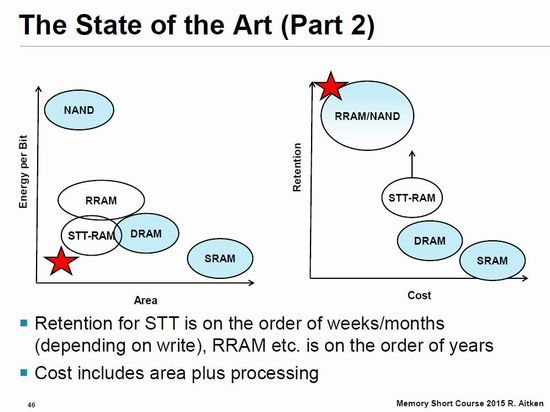

続いてシリコン面積とビット書き換えエネルギーのバランスで見ると、SRAMとNANDフラッシュの違いが良く分かる。SRAMはビット書き換えエネルギーが非常に低いにもかかわらず、シリコン面積では最も大きくなってしまう。逆にNANDフラッシュはシリコン面積が最も小さいにもかかわらず、ビット書き換えエネルギーが最も大きい。

この点でSTT-RAMとRRAMはいずれも、かなり良いバランスを保っている。シリコン面積はそこそこであり、書き換えエネルギーはNANDフラッシュに比べるとはるかに低い。

最後に製造コスト(シリコン面積とプロセスの両方を含む)とデータ保持時間のバランスを見ていこう。データ保持時間が長く、製造コストが低いのはNANDフラッシュとRRAMである。いずれもスーパーメモリの仕様をほぼ満足している。STT-RAMはデータ保持時間に改良の余地がある。

STT-MRAMとRRAMのいずれかが「スーパーメモリ」になるのか。それとも別の技術がこれから登場し、ダークホースとなるのか。あるいは、誰も最終勝者にはなれないのか。行方はまだ分からない。

⇒「福田昭のデバイス通信」連載バックナンバー一覧はこちら

関連記事

DRAMについて知っておくべき、4つのこと

DRAMについて知っておくべき、4つのこと

今回は、DRAMで知っておくべき4つの事実を紹介する。「DRAMの事業規模は巨大であること」「DRAMの性能は常に不足していること」「DRAM開発は傾斜が急になり続ける坂道を登っているようなものであること」「3次元技術はDRAM開発にとって援軍ではあるが救世主ではないこと」の4つだ。 “時代遅れのIC”で勝機をつかむ中国勢

“時代遅れのIC”で勝機をつかむ中国勢

今回紹介するD2Mのデジタル・フォトフレーム「Instacube」には、中国製のチップがぎっしりと詰まっている。なぜ、これらの中国メーカーはデザインウィンを得たのか。 磁気センサーの“異端児”がウェアラブルを変える

磁気センサーの“異端児”がウェアラブルを変える

超高感度磁気センサーの開発を手掛けるマグネデザインが、まったく新しい原理を採用した磁気センサー「GSR(GHz-Spin-Rotation)センサー」を開発した。現在最も普及している半導体センサーに比べて50倍の感度を実現している。 3D XPoint、開発から製造へ

3D XPoint、開発から製造へ

IntelとMicron Technologyが開発した「3D XPoint」は、製造の段階へと移る見込みだ。量産には12〜18カ月かかるとみられている。また、3D XPointでは、カルコゲナイド材料と「Ovonyx」スイッチが使われていることが明らかになった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待