キャパシターを忍ばせるパッケージ基板内蔵技術:コアレス基板にも対応

富士通インターコネクトテクノロジーズは、「JPCA Show 2016」(2016年6月1〜3日/東京ビッグサイト)で、同年5月23日に発表した薄膜キャパシター内蔵技術を展示した。

半導体の直下に設置可能

富士通インターコネクトテクノロジーズは、2016年6月1〜3日に東京ビッグサイトで開催されている「JPCA Show 2016」で、同年5月23日に発表した薄膜キャパシター(TFC:Thin Film Capacitor)内蔵技術を展示した。

電源の安定化に用いられるバイパスキャパシターは、高周波領域に対応するために大容量化が求められている。しかし、小型化が進む半導体パッケージでは、バイパスキャパシターがその外側や裏側に配置されるため、静電容量の確保が課題になっている。つまり、キャパシターを半導体により近い位置にする必要がある。

同技術は、バイパスキャパシターを半導体の直下となる基板の中に設置可能にし、高周波領域に対応した。また、階層構造のため実装面積/配線領域を有効に活用でき、小型化に貢献。動作電圧も安定化するため、消費電力の低減も期待できるという。

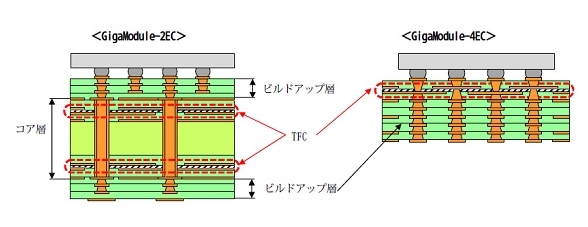

半導体サブストレートに使用される基板構造「GigaModule-EC」に適用され、2種類の構成が可能である。ビルドアップ基板のコア層に内蔵する「GigaModule-2EC」と、コアレス基板のビルドアップ層に内蔵する「GigaModule-4EC」だ。これにより、ハイエンド機器から小型のウェアラブル機器まで幅広く対応できるとしている。

「量産化に向けた発表は当社が初めて」

TFCはTDK製を活用しており、その静電容量は1.0μF/cm2、動作電圧は4.0V以下、内蔵後の部品の厚さは35μmとなっている。同技術では、TFCを2枚重ねることができるため、最大2.0μF/cm2の静電容量が得られる。

富士通インターコネクトテクノロジーズのビジネス開発室でプロジェクト部長を務める飯島和彦氏は、「次世代ハイエンドサーバ向けにサンプル基板の出荷を既に開始しており、2016年下期の量産化を予定している。TFCの内蔵技術は、7〜8年ほど前から学会で発表していたが、量産化に向けた発表をしたのは当社が初めてではないだろうか。まだコストは高いが、今後出荷が進んでいけば安くなるだろう」と語る。

同技術の開発には、富士通/富士通研究所/富士通アドバンストテクノロジの協力を得ている。TFC内蔵技術は、ソニーセミコンダクタソリューションズと開発したとする。

関連記事

GLOBALFOUNDRIES、22nm以降のFD-SOI開発に着手

GLOBALFOUNDRIES、22nm以降のFD-SOI開発に着手

GLOBALFOUNDRIESは、22nmプロセスを用いたFD-SOIのプラットフォーム「22FDX」の後継プラットフォームを開発中だという。とはいえ、最先端ICの世界では、FinFETが主流だ。GLOBALFOUNDRIESは、アナログ/RF回路ではFinFETよりもFD-SOIが適していると、FinFETに比べた時の利点を主張する。 半導体業界、“細分化”から“統合”へ

半導体業界、“細分化”から“統合”へ

半導体業界の歴史において、2015年ほど大規模な企業統合が繰り返された年はなかっただろう。ムーアの法則を維持すべく新しい技術を生み出してきた半導体業界では、どちらかといえば、企業は“細分化”する傾向にあったからだ。 ARMの10nmチップ、2016年末にもスマホに搭載か

ARMの10nmチップ、2016年末にもスマホに搭載か

ARMは2016年1月に、TSMCの10nm FinFETプロセス向けにSoC(System on Chip)のテストチップをテープアウトしたことを明らかにした。この10nm SoCは、2016年末までに携帯端末に搭載される予定だという。同プロセス技術は、比較的コストが高いが、低消費電力化に注力している。 室温でグラフェン回路をフレキ基板上に形成

室温でグラフェン回路をフレキ基板上に形成

米大学の研究チームが、室温環境でフレキシブル基板上にグラフェン回路を形成する技術を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

TFC内蔵技術の2つの構造 出典:富士通インターコネクトテクノロジーズ

TFC内蔵技術の2つの構造 出典:富士通インターコネクトテクノロジーズ