EE Times Japan >

プロセス技術 >

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(JSR Micro編):福田昭のデバイス通信(89)(2/2 ページ)

» 2016年09月21日 10時30分 公開

[福田昭,EE Times Japan]

5nm世代に向けた現状と課題

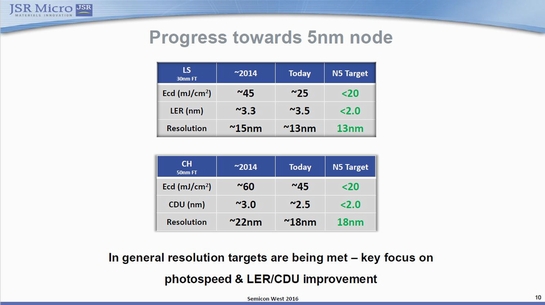

そしてさらに先の世代である5nm世代のEUVリソグラフィに向け、目標仕様と現状を示した。目標仕様には「感度(平方センチ当たりの露光エネルギー)」「パターンの品質(LWRあるいはCDU)」「解像力(ハーフピッチ)」の3つの項目がある。ラインアンドスペース(L&S)とコンタクトホール(CH)のそれぞれについて、数値を提示した。

L&Sの場合、解像力の目標仕様は13nmであり、既に達成しつつある。感度の目標仕様は20mJ以下で、現状の25mJからはさらに感度を高めなければならない。LWRの目標仕様は2.0nm以下である。現状のLWRである3.5nmとはかなり開きがあり、一層の改良が求められる。

CHの場合、解像力の目標仕様は18nmであり、既に達成しつつある。感度の目標仕様は20mJ以下で、現状の45mJとは大きな開きがある。大幅な改善が望まれる。CDU(Critical Dimention Uniformity:パターン寸法の均一性)の目標仕様は2.0nmであり、現状の2.5nmはかなり良いところまで来ている。あと少しの改良が必要だ。

(次回に続く)

⇒「福田昭のデバイス通信」バックナンバー一覧

関連記事

半導体プロセス技術、開発競争が過熱

半導体プロセス技術、開発競争が過熱

FinFETの微細化が進む一方で、FD-SOI(完全空乏型シリコン・オン・インシュレーター)にも注目が集まっている。専門家によれば、2025年までは28nm FinFETプロセスが優勢だとするが、それ以降はFD-SOIが伸びる可能性もある。 GF、12nm FD-SOIプロセス「12FDX」を発表

GF、12nm FD-SOIプロセス「12FDX」を発表

GLOBALFOUNDRIES(GF)が、22nmプロセスを用いたFD-SOI(完全空乏型シリコン・オン・インシュレータ)のプラットフォーム「22FDX」の後継となる次世代FD-SOIプロセス「12FDX」を発表した。GFによると、「10nm FinFETプロセスを超える性能を提供することが可能」とし、2019年の製造開始を計画する。 2020年、5nm世代でEUV時代が到来か

2020年、5nm世代でEUV時代が到来か

ASMLは2016年4〜6月にEUV(極端紫外線)リソグラフィ装置を4台受注し、2017年には12台を販売する計画を明かした。これを受けて業界では、EUV装置によるチップ量産が、5nmプロセス世代での製造が見込まれる2020年に「始まるかも」との期待感が広がっている。 FinFETサイズの物理的な限界は?

FinFETサイズの物理的な限界は?

ベルギーで開催された「IMEC Technology Forum(ITF) 2016」では、2.5D(2.5次元)のチップ積層技術や、FinFETのサイズの物理的な限界についても触れられた。 DRAMについて知っておくべき、4つのこと

DRAMについて知っておくべき、4つのこと

今回は、DRAMで知っておくべき4つの事実を紹介する。「DRAMの事業規模は巨大であること」「DRAMの性能は常に不足していること」「DRAM開発は傾斜が急になり続ける坂道を登っているようなものであること」「3次元技術はDRAM開発にとって援軍ではあるが救世主ではないこと」の4つだ。 Appleの新しいカスタムチップ3種を考察

Appleの新しいカスタムチップ3種を考察

Appleは2016年9月7日(米国時間)、「iPhone 7/iPhone 7 Plus」「Apple Watch Series 2」「AirPods」を発表した。そこにはそれぞれ、Apple独自のカスタムチップが採用される。これらのカスタムチップ「A10 Fusion」「W1」「S2」について、発表された情報を整理しつつ、どのようなものか見ていく。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR