多層プリント基板にICや受動素子などを内蔵する「ESP」技術:福田昭のデバイス通信(114) TSMCが解説する最先端パッケージング技術(13)(2/2 ページ)

» 2017年06月06日 11時30分 公開

[福田昭,EE Times Japan]

電源モジュールと高周波無線モジュールの小型化に寄与

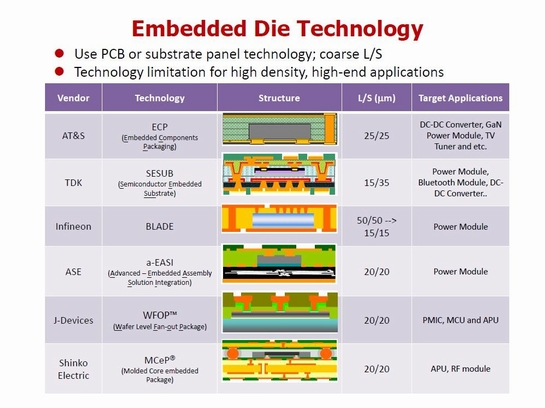

「ESP」、すなわち「部品内蔵基板」を利用したパッケージングは、半導体メーカーやパッケージング請負企業などが手掛けている。技術そのものはかなり古くからあり、いくつかの採用事例がある。

「部品内蔵基板」の応用分野で特徴的なのは、小型パワーモジュール(電源モジュール)や高周波無線モジュールなどでの採用が多いことだ。プロセッサそのものの採用は少ない。プロセッサに電源電圧を供給するモジュールの小型化を目的に、使われることが多い。

国内ではTDK、ジェイデバイス、新光電気工業などが、それぞれ独自の改良を加えた部品内蔵基板を手掛ける。なおジェイデバイスは、大型プリント基板を使ったパネルレベルの一括製造技術(FOPLP)の一環として、半導体チップをプリント基板に内蔵する技術「WFOP(Wafer Level Fan-out Packaging)」を開発していた。

海外ではAT&S(Austria Technologie & Systemtechnik AG)、Infineon Technologies(関連記事:IC埋め込みパッケージで高効率/高放熱性を実現)、ASE(Advanced Semiconductor Engineering)などが、部品内蔵基板を手掛ける。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

(次の記事を読む)

関連記事

3次元集積化(3D IC)の理想と現実

3次元集積化(3D IC)の理想と現実

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。 EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

2017年5月31日、来日したGLOBALFOUNDRIES(グローバルファウンドリーズ/GF)CMOSプラットフォーム事業部シニアバイスプレジデントのGregg Bartlett氏に7nm FinFET、12nm FD-SOIの開発状況などについてインタビューした。 シリコンが次の手、村田製作所のキャパシター戦略

シリコンが次の手、村田製作所のキャパシター戦略

2016年10月に村田製作所が買収したフランスのIPDiAは、シリコンキャパシターを事業として手掛けるほぼ唯一のメーカーだ。積層セラミックコンデンサーに比べてかなり高価なシリコンキャパシターは、その用途は限られている。それにもかかわらず、なぜ村田製作所はIPDiAの買収に至ったのか。 TSMCの7nm FinFET、2017年4月には発注可能に?

TSMCの7nm FinFET、2017年4月には発注可能に?

TSMCは米国カリフォルニア州サンノゼで開催されたイベントで、7nm FinFETプロセス技術について言及した。3次元(3D)パッケージングオプションを強化して、数カ月後に提供を開始する計画だという。 TSMC、中国 南京に半導体製造工場を建設

TSMC、中国 南京に半導体製造工場を建設

TSMCが、中国の南京に12インチウエハー工場を設立するとして、台湾の投資委員会に申請書を提出した。世界最大規模の半導体市場でありながら、半導体のほとんどを輸入に頼っている中国の強い需要を取り込む考えだ。 SanDiskが語る、抵抗変化メモリの電気伝導メカニズム

SanDiskが語る、抵抗変化メモリの電気伝導メカニズム

今回は、抵抗変化メモリ(ReRAM)の記憶素子における電気伝導の原理について解説する。主な原理は7種類あるが、ReRAMの「高抵抗状態」と「低抵抗状態」を作り出すには、同じ原理が使われるとは限らないことも覚えておきたい。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR