強誘電体トランジスタで多値メモリを実現する(後編):福田昭のストレージ通信(79) 強誘電体メモリの再発見(23)

前編に続き、二酸化ハフニウム系強誘電体材料を使った強誘電体トランジスタ(FeFET)で多値メモリを実現する仕組みを解説する。特に、2つのドメインで構成されたFeFETの長期信頼性の評価に焦点を当てる。

3つのドメインによって2ビットのデータを1個のトランジスタに記憶

本シリーズの前編では、新材料である「二酸化ハフニウム系強誘電体材料」を使った強誘電体トランジスタ(FeFET)で、多値メモリを実現する手法をご紹介した。トランジスタの強誘電体薄膜を複数の微小な分極単位領域(分域:ドメイン)で構成することによって、ドメインごとに分極反転を制御する。ドメインごとに分極反転を独立に制御することで、しきい電圧を段階的に変えられるようになる。

例えば3つのドメインで構成された強誘電体トランジスタだと、トランジスタのしきい電圧を4通りに変えられる。すなわち2ビット(4値)のデータを1個のトランジスタで記憶可能になる。本シリーズの前編では、NaMLabおよびドレスデン工科大学などの共同研究グループが実際に、3つのドメインによって2bitを記憶するトランジスタを昨年(2016年)に試作発表したことをご報告した。

2つのドメインで構成した多値トランジスタの長期信頼性を評価

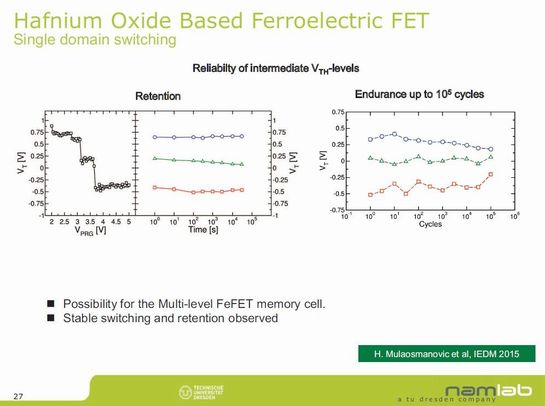

NaMLabおよびドレスデン工科大学などの共同研究グループは、2つのドメインによって3通りのしきい電圧を記憶する強誘電体トランジスタを二酸化ハフニウム薄膜で試作し、長期信頼性(データ保持期間と書き換えサイクル寿命)を評価した結果を、一昨年(2015年)に国際学会IEDMで発表済みである。

ゲートの寸法は長さが30nm、幅が80nm。二酸化ハフニウムの膜厚は10nm、二酸化ハフニウムとシリコン基板の間はシリコン酸化窒化膜で厚みは1.2nmである。ゲート電極は多結晶シリコンと窒化チタンの多層膜で、厚みは8nm。プログラム電圧は2.5V〜5Vとかなり低い。しきい電圧の範囲は+0.75V〜−0.75Vである。

3通りのしきい電圧を記憶した強誘電体トランジスタの長期信頼性。左のグラフはプログラム電圧としきい電圧、データ保持期間。室温で10時間を経過しても、劣化は見られない。右のグラフは書き換えサイクル寿命。105回まで確認した。出典:NaMLabおよびドレスデン工科大学(クリックで拡大)

3通りのしきい電圧を記憶した強誘電体トランジスタの長期信頼性。左のグラフはプログラム電圧としきい電圧、データ保持期間。室温で10時間を経過しても、劣化は見られない。右のグラフは書き換えサイクル寿命。105回まで確認した。出典:NaMLabおよびドレスデン工科大学(クリックで拡大)データ保持期間は室温で10時間まで確認した。目立った劣化は現れていない。書き換えサイクル寿命は105回(10万回)まで確認した。102回(100回)を超えたあたりから、徐々に劣化が始まっている。あまり良い特性だとは言い難い。

この他、ゲートの寸法が長さ90nm、幅80nmと大きな強誘電体トランジスタを試作し、2.5V〜5Vのプログラム電圧で、しきい電圧が6段階に変化することを確認できた。このことも2015年に国際学会IEDMで発表されている。

これらの性能数値は当然ながら、実用レベルとは相当な開きがある。ただし、改良の余地を十分に秘めた値でもある。今後の研究の進展が、大いに期待できると言えよう。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

SanDiskが語る、抵抗変化メモリのセルアレイとセルの選択

SanDiskが語る、抵抗変化メモリのセルアレイとセルの選択

今回は、半導体メモリのメモリセルアレイと、アレイから特定のメモリセルを選択する手段について説明する。 「HDDが壊れる」まで(前編)

「HDDが壊れる」まで(前編)

HDDは壊れやすい製品だ。では、どれぐらい壊れやすいのか。HDDの寿命は仕様書にあるどの数字を見れば分かるのだろうか。平均故障間隔(MTBF)にまつわる勘違いを正しながら解説した。 TSMC、7nm/EUVの開発状況をアップデート

TSMC、7nm/EUVの開発状況をアップデート

TSMCは2017年9月、米国で開催されたイベントで7nmプロセス技術やEUV(極端紫外線)リソグラフィの開発状況などを説明した。 東芝、日米韓連合にメモリ事業を売却

東芝、日米韓連合にメモリ事業を売却

東芝は、東芝メモリ(TMC)の売却契約を、日米韓企業連合と締結したと発表した。 2016年半導体業界の研究開発費トップ10、東芝5位

2016年半導体業界の研究開発費トップ10、東芝5位

IC Insightsは、2016年の半導体業界における研究開発費メーカー別ランキングを発表した。 モバイル端末向けの最先端パッケージング技術

モバイル端末向けの最先端パッケージング技術

今回から、モバイル端末向けのパッケージング技術について解説する。大きく分けて、ウエハーレベルのファンアウトパッケージング(FOWLP)、パネルレベルのファンアウトパッケージング(FOPLP)、プリント基板へ回路素子を埋め込むパッケージング(ESP)がある。まずは、パッケージング技術における「ファンアウト」の意味を確認しつつ、Infineon Technologiesが開発した“元祖FOWLP”を説明したい。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 東芝との協議やデンソー提案への対応、ロームが新声明

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入