IEDM 2017の講演2日目(12月5日)午後(その1):記憶密度を2倍に高める3D NAND技術:福田昭のデバイス通信(121) 12月開催予定のIEDM 2017をプレビュー(5)(2/2 ページ)

» 2017年11月21日 11時30分 公開

[福田昭,EE Times Japan]

5nm以降のCMOS技術とトランジスタ技術を議論

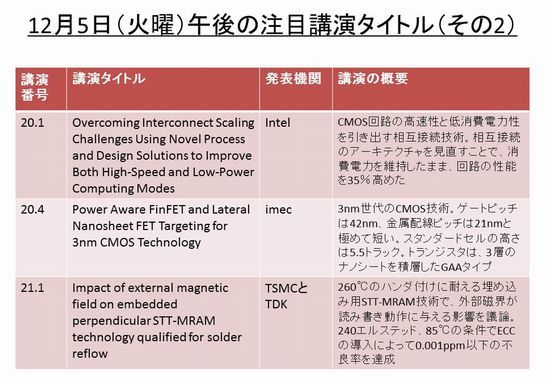

セッション20も、興味深い講演が少なくない。5nm以降のCMOS技術とトランジスタ技術に関する研究成果が続出する。

Intelは、CMOS回路の高速性と低消費電力性を引き出す相互接続技術を議論する(講演番号20.1)。微細化が進んだ結果、トランジスタよりも相互接続が回路の性能を制限するようになってきたことが背景にある。相互接続のアーキテクチャを見直すことで、消費電力を維持したまま、回路の性能を35%高めることができた。

GLOBALFOUNDRIESはFinFETのフィン幅を1.6nmと微細化したロジックとSRAMを発表する(講演番号20.2)。フィン幅を縮めていったときの利点と弱点を議論する。

imecは、3nm世代のCMOS技術を発表する(講演番号20.4)。ゲートピッチは42nm、金属配線ピッチは21nmと極めて短い。スタンダードセルの高さは5.5トラック。トランジスタは、3層のナノシートを積層したゲートオールアラウンド(GAA)タイプである。GAAの導入によってFinFETに比べて微細化を緩和した状態で同じトランジスタ性能を実現できることを示す。

この他、TSMCとTDKの共同開発チームが、260℃のハンダ付けに耐える埋め込み用STT-MRAM技術を発表する(講演番号21.1)。外部磁界が読み書き動作に与える影響を議論した。240エルステッド、85℃の条件でECC(誤り訂正符号)の導入によって0.001ppm以下の不良率を達成している。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

IEDM 2017の全体スケジュールと基調講演

IEDM 2017の全体スケジュールと基調講演

ことしも「IEDM」の季節がやってきた。最先端電子デバイスの研究開発に関する国際学会「IEDM 2017」が、12月に米国で開催される。本シリーズでは、概要と注目の技術講演を紹介していく。 NVIDIAがエネルギー効率の高い相互接続チップを試作

NVIDIAがエネルギー効率の高い相互接続チップを試作

相互接続(インターコネクト)のエネルギー効率を高める技術の1つである「バランス型電荷再利用バス(BCRB:Balanced Charge Recycling Bus)」。今回は、BCRB技術のバスを搭載したテストチップの概要と、実験結果について解説する。 パッケージング技術がワンチップ化の限界を突破

パッケージング技術がワンチップ化の限界を突破

システムを複数のチップに分けてから高密度に集積化したパッケージは、SiP(System in Package)と呼ばれる。「ムーアの法則」を拡張するために、新しいSiP技術あるいはパッケージング技術が次々に登場している。今回から始まる新シリーズでは、こうした新しいパッケージング技術を紹介したい。 「不揮発性DRAM」へのアプローチ(前編)

「不揮発性DRAM」へのアプローチ(前編)

今回から、「不揮発性DRAM」の実現を目指す研究開発について解説する。二酸化ジルコニウムは、その結晶構造から、工夫次第で強誘電体のような不揮発性を付加できる可能性がある。 ムーアの法則の終息でIDMの時代に“逆戻り”か?

ムーアの法則の終息でIDMの時代に“逆戻り”か?

米国サンフランシスコで開催されたコンピュータ関連のイベントで、半導体業界の専門家たちがパネルディスカッションを行い、「ムーアの法則」を中心に業界の今後について議論した。専門家の1人は、Appleの動きや、近年の大規模なM&Aの動きから、半導体業界はIDM(垂直統合型)に近い形に“逆戻り”するのだろうか、との疑問を投げかけた。 ムーアの法則、半導体業界はどう捉えるべきか(前編)

ムーアの法則、半導体業界はどう捉えるべきか(前編)

台湾Etron TechnologyのCEOであるNicky Lu氏は、「ムーアの法則」は、技術開発の方針としての役目を既に終え、ビジネス的な意味合いの方が強くなっていると述べる。半導体メーカーが今、ムーアの法則について認識すべきこととは何なのか。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険

Special SitePR

あなたにおすすめの記事PR