半導体メモリのチップとパッケージとシリコンダイ(後編):福田昭のデバイス通信(140)(2/2 ページ)

製品が内蔵するシリコンダイの枚数を知る方法

それでは、DRAMやフラッシュメモリなどが内蔵しているシリコンダイの「枚数」を知る方法は、あるのだろうか。結論から先に述べてしまうと、シリコンダイの枚数を知る方法は「ある」。大きく分けると2つの方法、すなわち比較的簡単な方法と、やや複雑な方法がある。

比較的簡単な方法は、半導体メモリベンダーのWebサイトで、製品情報を見ることである。ベンダーによっては製品情報に、パッケージに内蔵したシリコンダイの枚数を記述している。

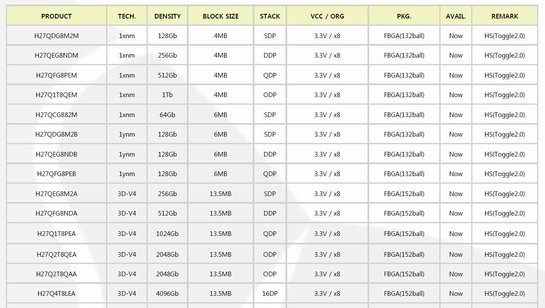

例えばSK HynixのWebサイトからは、NAND型フラッシュメモリ製品の一覧表(データブック、PDF形式)をダウンロードできる。一覧表には、「スタック(STACK)」と書かれている項目があり、先ほど説明したSDPやDDPなどの名称が記載されている。この名称から、シリコンダイの枚数が分かる。

SK HynixのNANDフラッシュメモリ製品データブック。TLCタイプの製品ページの一部を拡大表示した。中央に「STACK」の項目があり、SDPやDDPなどのシリコンダイの枚数(積層数)を示す情報が開示されている

SK HynixのNANDフラッシュメモリ製品データブック。TLCタイプの製品ページの一部を拡大表示した。中央に「STACK」の項目があり、SDPやDDPなどのシリコンダイの枚数(積層数)を示す情報が開示されているやや複雑な方法は、半導体メモリベンダーのWebサイトから、製品のデータシートを入手して、製品番号の定義を調べることである。製品番号はアルファベットと数字の羅列であり、それぞれの文字が意味を有している。その中に、シリコンダイの枚数に関する情報がある。

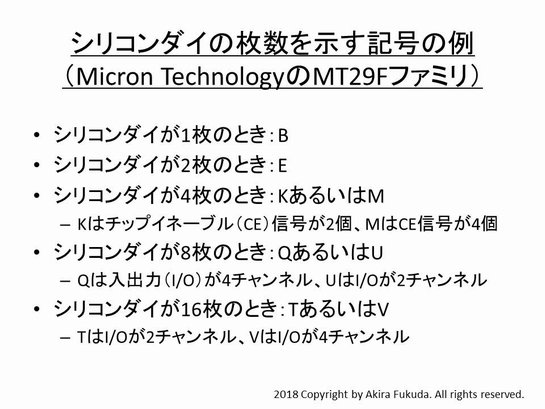

例えばMicron TechnologyのMLC方式NANDフラッシュメモリ「MT29F」ファミリーのデータシートは、製品番号の定義(Part Numbering Information)の中に、シリコンダイの枚数を示す記号を明記している。データシートはページ数が多く、200ページから300ページに及ぶことが珍しくない。また製品番号は桁数が10桁〜20桁と多く、複雑ではある。このため、調べるのにはいささかの手間を必要とする。

「MT29F」ファミリーの製品番号情報(Part Numbering Information)から、シリコンダイの枚数に関する記号を抜粋したもの。シリコンダイが同じ枚数の製品でも、チップイネーブル(CE)信号の個数や入出力のチャンネル数などの違いにより、異なる記号が割り当てられている

「MT29F」ファミリーの製品番号情報(Part Numbering Information)から、シリコンダイの枚数に関する記号を抜粋したもの。シリコンダイが同じ枚数の製品でも、チップイネーブル(CE)信号の個数や入出力のチャンネル数などの違いにより、異なる記号が割り当てられているただし最近は、顧客あるいは顧客候補としての登録を済ませないと、データシートを入手できないことがある。そうなった場合は、公開情報からシリコンダイの枚数を知ることは難しい。

(次の記事を読む)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

半導体メモリのチップとパッケージとシリコンダイ(前編)

半導体メモリのチップとパッケージとシリコンダイ(前編)

「チップ」「デバイス」という単語から想像するイメージは、業界やコミュニティーによってずれがある。では、どのようなずれがあり、なぜ、ずれが生じたのだろうか。 Samsung、10nmクラスの8Gb DDR4 DRAMを量産開始

Samsung、10nmクラスの8Gb DDR4 DRAMを量産開始

Samsung Electronicsが、10nmクラスのプロセスを採用した第2世代の8GビットDDR4 DRAMの量産を開始したと発表した。 半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

2008〜2017年まで主に米国で開催されてきた「国際メモリワークショップ(IMW)」が、2018年は日本の京都で開催される。今回はIMWの概要を紹介しよう。 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。 モバイル端末向けの最先端パッケージング技術

モバイル端末向けの最先端パッケージング技術

今回から、モバイル端末向けのパッケージング技術について解説する。大きく分けて、ウエハーレベルのファンアウトパッケージング(FOWLP)、パネルレベルのファンアウトパッケージング(FOPLP)、プリント基板へ回路素子を埋め込むパッケージング(ESP)がある。まずは、パッケージング技術における「ファンアウト」の意味を確認しつつ、Infineon Technologiesが開発した“元祖FOWLP”を説明したい。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す