EE Times Japan >

先端技術 >

エッジAIを安価・高速に、FPGAを駆使するベンチャー:どんなモノにも深層学習を実装(2/2 ページ)

» 2018年09月04日 11時30分 公開

[松本貴志,EE Times Japan]

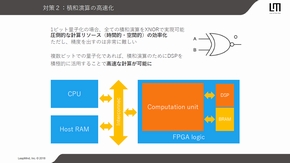

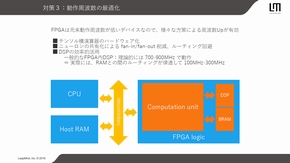

モデルをFPGAに実装する技術にも強み

さらに、モデルをFPGAに実装するにあたり各種の方策を凝らしたとする。積和演算にDSPを活用することによる演算高速化や、テンソル積演算器のハードウェア化などによる動作周波数の最適化、テンソルをハードウェアサイズに合わせて分割し多重ループの最適化などを実施した。

また、イベントではDeLTA-Familyを実装したFPGAデバイスによる実機デモを展示。安村氏は、「ディープラーニングによる顔認識アプリケーションをArmアーキテクチャのCPUで実行した場合は、0.6フレーム/秒(fps)程度の速度にとどまってしまう。DeLTA-Familyを活用すれば、ローエンドなFPGAデバイスでも10fps程度のスムーズな動作を実現できる」として、同社ソリューションの優位性を強調した。

関連記事

応用例で見る、ルネサスの組み込みAI

応用例で見る、ルネサスの組み込みAI

AI(人工知能)機能を持つ組み込み機器の登場が、スマートな社会を身近なものとする。ルネサス エレクトロニクスはセキュアで自律的に動作する組み込み機器を開発するための「e-AIソリューション」を提案する。 Intel、“組み込みAIチップ”のPC搭載を狙う

Intel、“組み込みAIチップ”のPC搭載を狙う

Intelは、CPUの他に、Movidiusが手掛けてきたVPU(Vision Processing Unit)のような推論チップを、PCに搭載することを目指しているようだ。 IoTでの使いやすさを追求、組み込みプラットフォーム

IoTでの使いやすさを追求、組み込みプラットフォーム

アットマークテクノは、「第7回 IoT/M2M展【春】」で、産業用組み込みプラットフォーム「Armadillo-640」や国内3キャリア対応のIoT(モノのインターネット)ゲートウェイ「Armadillo-IoT」などについてデモ展示した。 ルネサス MCU/MPUのAI処理性能を今後3年で1000倍に

ルネサス MCU/MPUのAI処理性能を今後3年で1000倍に

ルネサス エレクトロニクスはMPU/MCU製品のAI(人工知能)処理性能を今後3年ほどで1000倍に高めるとの方針を明らかにした。 Armの独壇場にはならない? AI向けコア市場

Armの独壇場にはならない? AI向けコア市場

CPUコアにおいて、多くの分野で高いシェアを誇るArmだが、AI(人工知能)エンジン向けチップのコアでは、独壇場とはいかないようだ。 NVIDIAが解説するディープラーニングの基礎(前編)

NVIDIAが解説するディープラーニングの基礎(前編)

エヌビディアは2018年4月24日、ディープラーニングに関するセミナー「NVIDIA Deep Learning Seminar 2018」を東京都内で開催した。本稿では、セッション「これから始める人のためのディープラーニング基礎講座」から、ディープラーニングの歴史や概要、学習の流れについて紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 全固体電池の製造プロセス簡素化、東北大が新手法

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

Special SitePR

あなたにおすすめの記事PR

ディープラーニングによる顔認識アプリケーションを行うデモの様子。写真撮影時、9.9fpsで動作していた

ディープラーニングによる顔認識アプリケーションを行うデモの様子。写真撮影時、9.9fpsで動作していた