メモリセルアレイのベースとなるマルチペア薄膜の形成:福田昭のストレージ通信(119) 3D NANDのスケーリング(7)(2/2 ページ)

» 2018年10月22日 10時30分 公開

[福田昭,EE Times Japan]

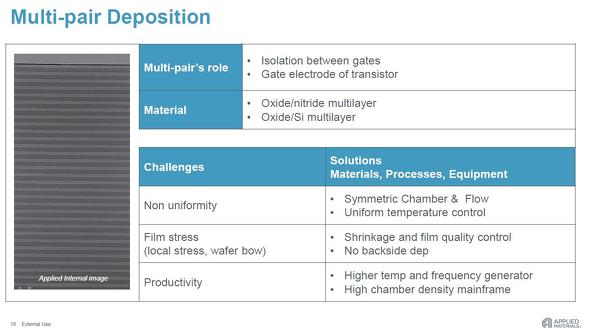

高均一で低応力のペア薄膜を高速に堆積

ペア薄膜には主に、異なる2つのタイプがある。1つは、酸化膜と多結晶シリコン膜のペアである。酸化膜が隣接セル間の絶縁層、多結晶シリコン膜が制御ゲート層となる。もう1つは、酸化膜と窒化膜のペアである。酸化膜は隣接セル間の絶縁層となる。窒化膜はいわゆる犠牲層で、エッチングで除去したあとに制御ゲートの金属層を埋め込むことになる。

マルチペア薄膜の成膜に要求される項目(課題)には、高い均一性、応力(ストレス)の排除、高い生産性(高スループット)などがある。高い均一性を得るには、成膜用チャンバー間のばらつきの低減、成膜用ガスの流路制御、高い精度の温度管理などが求められる。

次の課題は応力の排除である。マルチペア薄膜では局所的に応力が集中することがある。薄膜の品質を管理し、さらにはウエハー裏面における不要な薄膜生成(バックサイドデポジション)を抑制することが求められる。

最後の課題は、生産性の向上である。48ペア、32ペアといった数多くのマルチペア薄膜の堆積では、堆積時間をなるべく短くすることが求められる。マルチチャンバー成膜装置のチャンバー数を増やす、成膜速度を高めるといったこと手法が考えられる。ただしチャンバー数の増加と成膜速度の高速化はいずれも、マルチペア薄膜の均一性を低下させる恐れがある。トレードオフに留意しなければならない。

マルチペア薄膜形成(Multi-pair Deposition)技術の概要。左の写真は、形成したマルチペア薄膜の断面を電子顕微鏡で観察した画像。右上の表は技術の目的と材料、右下の表は技術の課題と解決策。出典:Applied Materials(クリックで拡大)

マルチペア薄膜形成(Multi-pair Deposition)技術の概要。左の写真は、形成したマルチペア薄膜の断面を電子顕微鏡で観察した画像。右上の表は技術の目的と材料、右下の表は技術の課題と解決策。出典:Applied Materials(クリックで拡大)(次回へ続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

3D NANDフラッシュ製造のカギとなるプロセス技術

3D NANDフラッシュ製造のカギとなるプロセス技術

今回は、3D NANDフラッシュメモリの製造プロセスにおける重要な技術(キープロセス)について解説する。 3D NANDフラッシュメモリの断面構造と製造工程

3D NANDフラッシュメモリの断面構造と製造工程

2018年5月に開催された国際会議「IMW」で行われたセミナー「3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望」の概要をシリーズで紹介している。今回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を解説しよう。 膨張を続けるデジタルデータをNANDフラッシュが貯蔵

膨張を続けるデジタルデータをNANDフラッシュが貯蔵

2018年5月に開催された「IMW(International Memory Workshop)」のショートコースで行われた技術講座から、「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」の概要をシリーズでお届けする。 理研、パルス電流で超電導状態の制御に成功

理研、パルス電流で超電導状態の制御に成功

理化学研究所(理研)の研究チームは、パルス電流を用いて「超電導状態」の生成と消去に成功した。書き換え可能な超電導量子コンピュータ向け回路の実現につながる可能性が高い。 単分子誘導体を開発、記録密度を1000倍以上に

単分子誘導体を開発、記録密度を1000倍以上に

広島大学の研究チームは、室温で強誘電性(メモリ効果)を示す「単分子誘導体(SME:Single Molecule Electret)」の開発に成功した。記録密度を従来の1000倍以上に向上させることが可能となる。 「3D XPoint」、Intelは強気もMicronは手を引く?

「3D XPoint」、Intelは強気もMicronは手を引く?

IntelとMicron Technology(以下、Micon)が、共同開発プログラムを終了する予定であると発表した。両社が共同開発しているメモリ「3D XPoint」の将来に何が待ち受けているのかは、誰にその問いかけをするかによって答えが異なるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR