最先端のドライエッチング技術−マルチ・パターニングとHARC−:湯之上隆のナノフォーカス(5) ドライエッチング技術のイノベーション史(5)(5/5 ページ)

HARCのキーパラメータは温度

ラジカルの付着係数は、温度が低くなると大きくなる。逆に言えば、温度を上げれば、ラジカルは孔の側壁に付着しにくくなる。

そこで、孔加工を開始し、孔が深くなるとともに、静電チャックと呼ばれるウエハのステージの温度を少しずつ上げていくと、孔底までラジカルを供給できるようになる。

それなら、最初から静電チャックを高温にして、HARC加工を行えば良いと思われるかもしれない。しかし、そうすると、孔の側壁にラジカルや反応生成物がまったく付着せず、孔の横方向にエッチングが進んでしまい、孔が樽型に形成されてしまう。この現象を、ボーイングと呼んでいる。

ボーイングを防ぐためには、少しだけラジカルや反応生成物を孔の側壁に付着させ、これを保護膜として横方向のエッチングを防ぐことが有効である。すなわち、ボーイングを起こさず、次第に深くなる孔底へラジカルを供給するためには、少しずつ温度を上げていくことが必要となる。

また、孔が深くなると、反応生成物がうまく排気されず、孔底にたまってしまい、エッチストップが起きる場合もある。その際は、酸素プラズマのエッチングにより、反応生成物を除去する。これを、「O2フラッシュ」と呼んでいる。

さらに、上記のエッチストップを防ぐために、ラジカルの供給、イオン照射、反応生成物の排気、これらをサイクリックに行うという手法も検討されている。

以上をまとめると、高AR比のHARC加工のキーパラメータは、温度である。温度のデリケートな制御が、真っすぐで深いHARC加工を可能にする。

3次元NANDのメモリホール用HARC加工では、米Lam Researchがシェアを独占している。それは、Lam Researchのドライエッチング装置が、温度の精密な制御ができることに起因している。

最先端のドライエッチング技術の総括

ドライエッチングの最先端技術として、マルチ・パターニングとHARC加工を詳述した。

ダブル・パターニングでは、露光工程は1回しかないが、ドライエッチング工程が、スリミングも含めると6回もある。クアドロプル・パターニングでは、ドライエッチング工程が8回に増える。

また、3次元NANDのメモリホール用HARCでは、64層でAR比が約65になる。そのHARC加工には1枚のウエハで約1時間かかるという。ドライエッチング装置1チャンバで1日に1ロット(25枚)しか処理できない。

従って、月産10万枚規模の量産工場では、毎日3333枚(133ロット)を処理しなくてはならないため、メモリホールだけで最低133チャンバー、メンテナンスを考慮すれば150〜200チャンバーが必要になる。その他にメモリセル周りには、メモリホール用の分厚いハードマスクの加工、ゲートトレンチの加工、階段状のコンタクトホールの加工がある。恐らく合計で、400〜500チャンバーが必要になるだろう。

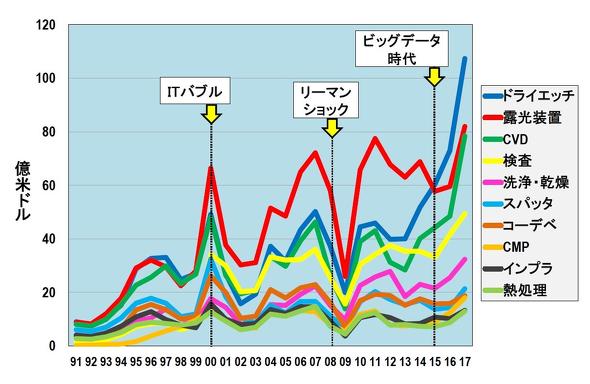

以上のように、マルチ・パターニングが普及し、NANDが3次元化して途轍もない台数のドライエッチング装置が必要になったため、2017年に、それまでトップだった露光装置市場を、ドライエッチング市場が上回ったわけだ(図10)。

そのドライエッチングでは現在、原子層を一層ずつエッチングする“アトミックレイヤーエッチング(Atomic Layer Etching、ALE)の研究開発が大ブームとなっている。次回の最終回では、ALEを取り上げるとともに、ドライエッチング技術の未来を展望したい。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。

有門経敏(ありかど つねとし)Tech Trend Analysis代表

1951年生まれ。福岡県出身。大阪大学大学院博士課程(応用化学専攻)を修了後、東芝入社。2001年、半導体先端テクノロジーズ出向を経て、2004年、東京エレクトロン入社。技術マーケテイングと開発企画を担当。現在、Tech Trend Analysisの代表として産業や技術動向の分析を行っている。

関連記事

遅れていたIntelの10nmチップ、出荷開始のメドが立つ

遅れていたIntelの10nmチップ、出荷開始のメドが立つ

Intelは、「10nmプロセスの歩留まりの改善を進めている」と述べ、2019年のホリデーシーズンまでに10nmチップを出荷する計画をあらためて表明した。 チャージングダメージの障壁を乗り越えた日米の情熱

チャージングダメージの障壁を乗り越えた日米の情熱

1980年代初旬、プラズマを用いたエッチング技術は、チャージングダメージという大きな壁に直面した。だが、日米によるすさまじい研究の結果、2000年までにほぼ全ての問題が解決された。本稿では、問題解決までの足跡をたどる。 Samsung、EUV適用7nmチップ開発を加速

Samsung、EUV適用7nmチップ開発を加速

ファウンドリーの間で現在、EUV(極端紫外線)リソグラフィを使用した業界初となる半導体チップを実現すべく、競争が繰り広げられている。Samsung Electronics(以下、Samsung)は、「EUVリソグラフィを適用した複数の7nmプロセスチップをテープアウトした」と発表した。 ASML、EUVシステムを2019年に30台出荷する見通し

ASML、EUVシステムを2019年に30台出荷する見通し

ASMLが2018年7月18日(オランダ時間)に発表したところによると、同社は2018年に20台のEUV(極端紫外線)露光システムを、2019年には少なくとも30台を出荷する予定だという。 GLOBALFOUNDRIES、7nm開発を無期限停止へ

GLOBALFOUNDRIES、7nm開発を無期限停止へ

最先端の半導体プロセス技術をめぐる競争は、今や3社に絞られた。GLOBALFOUNDRIESは、7nm FinFETプロセスの開発を無期限に延期すると発表した。 Samsung、3nm「GAA FET」の量産を2021年内に開始か

Samsung、3nm「GAA FET」の量産を2021年内に開始か

Samsung Electronicsは、米国カリフォルニア州サンタクララで2018年5月22日(現地時間)に開催したファウンドリー技術の年次フォーラムで、FinFETの後継アーキテクチャとされるGAA(Gate All Around)トランジスタを2021年に3nmノードで量産する計画を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長