Cypress、新世代車載マイコン「Traveo II」を発表:点ではなく、面で攻める(2/2 ページ)

第1弾は、8Mバイトフラッシュ搭載した動作周波数350MHz品など3シリーズ

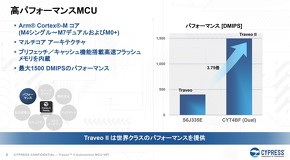

この日、発表したTraveo IIは、主にボディ制御用途向けの3シリーズ。8Mバイト容量のフラッシュメモリを内蔵し、最大動作周波数350MHzのArm Cortex-M7コアを2個搭載する「CYT4BFシリーズ」と、最大動作周波数160MHzのArm Cortex-M4コアを搭載する「CYT2B7シリーズ」(フラッシュ容量1Mバイト)と「CYT2B9シリーズ」(フラッシュ容量2Mバイト)の3シリーズだ。今後、Arm Cortex-M7を1個搭載するシリーズや、Arm Cortex-M4のシングルコア構成でよりフラッシュメモリ容量が小さい製品シリーズもボディ制御用途向けに拡充する。さらに、第1世代Traveoの主力用途の一つだったクラスタ用途に向けたグラフィックスエンジンを搭載したシリーズも開発、展開するという。

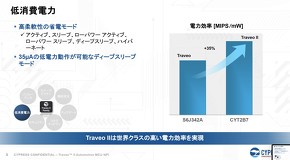

電力当たりの処理性能については、CYT2B7シリーズで第1世代Traveoよりも35%向上したという。またディープスリープモード時の消費電流も第1世代Traveoの50μAから35μAにまで低減したという。

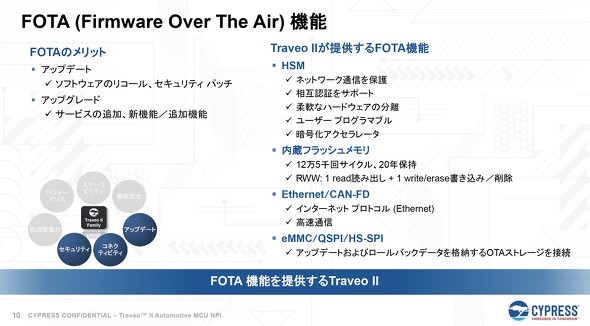

OTA(Over The Air)に対応

Traveo IIでは、無線経由でファームウェアのアップデートが行えるOTA(Over The Air)機能に対応する点も特長。具体的には、動作を止めることなくファームウェアアップデートを行えるようメモリ領域を2つに分割する機能や、セキュアなアップデートを実現するための暗号化アクセラレータなどを持つHSM(Hardware Security Module)を備える。なお、Traveo IIでは、セキュア機能の処理を行うために、メインのCPUコアとは別にArm Cortex-M0+コアを搭載し「高度なセキュア処理が行える」としている。

関連記事

サイプレス、Bluetooth mesh対応のMCUを開発

サイプレス、Bluetooth mesh対応のMCUを開発

サイプレス セミコンダクタは、IoT(モノのインターネット)機器向けにBluetooth meshネットワーク対応のBluetooth 5.0/Bluetooth Low Energy(BLE)マイクロコントローラ(MCU)「CYW20819/CYW20820」を開発した。 機器に搭載するだけで、給電方式がUSB Type-C PDに

機器に搭載するだけで、給電方式がUSB Type-C PDに

Cypress Semiconductor(以下、Cypress)は、ドイツ・ニュルンベルクで開催中の組み込み技術の展示会「embedded world 2019」(2019年2月26〜28日)で、さまざまな電化製品に使われている電源アダプターから、USB Type-C PD(Power Delivery)による給電方式へと変換するポートコントローラー「EZ-PD Barrel Connector Replacement(BCR)」のデモを展示した。 国内車載半導体シェア3位目指し、MCU拡販を強化

国内車載半導体シェア3位目指し、MCU拡販を強化

Infineon Technologies(日本法人:インフィニオン テクノロジーズ ジャパン)は2019年1月16日、展示会「第11回オートモーティブワールド」会場で、車載マイコン事業に関する記者説明会を開催し、日本での車載マイコン(MCU)販売の展開を本格化させ、日本国内における車載半導体シェアを高めるとの方針を打ち出した。 NXPが新車載マイコン第1弾として800MHz、64MB品

NXPが新車載マイコン第1弾として800MHz、64MB品

NXP Semiconductorsは2018年6月19日、新しい車載用マイクロプロセッサ(MPU)/マイクロコントローラ(MCU)製品群「S32」の第1弾製品として、安全走行制御(セーフティ制御)システム向けのハイエンドMPU/MCU「S32S」を発表した。動作周波数800MHzのArm cortex-R52コアを8個と、最大64Mバイト(MB)の大容量フラッシュメモリを搭載するハイエンドMPU/MCUで、次世代の安全走行制御用途に向けるという。 車載用マイコンが内蔵する不揮発性メモリ

車載用マイコンが内蔵する不揮発性メモリ

今回から数回にわたり、2017年12月に開催された「IEDM」で行われた車載用の埋め込み不揮発性メモリに関する講座の模様を紹介していく。 ルネサス、2020年にTSMCで28nmマイコンを量産へ

ルネサス、2020年にTSMCで28nmマイコンを量産へ

ルネサス エレクトロニクスは2016年9月、28nmプロセスを用いたフラッシュ内蔵マイコンを2017年にサンプル出荷、2020年から量産すると発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk