Intelが3つの次世代パッケージング技術を明らかに:SEMICON West 2019(2/2 ページ)

基板からチップにTSVで電力供給できるインターコネクト技術

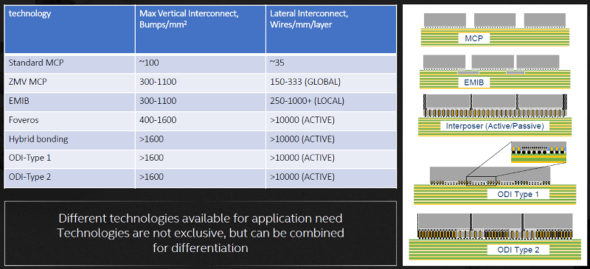

3つ目の「Omni Directional Interconnect(ODI)」は、パッケージ内のチップレット間通信をより柔軟にするためのインターコネクト技術だ。TSV(シリコン貫通ビア)を介して、パッケージ基板から、その上に実装されているチップに電力も供給できる。ただし、今のところまだ研究プロジェクトの段階にあるという。

チップの積層は現在、より大規模で高速なデバイスを提供する上で最も重要な手段の一つとされている。TSMCはこれまで何年も、スマートフォン向けSoC(System on Chip)からハイエンドFPGA、GPU、通信ASICに至るまで、さまざまな形式のチップ積層技術を適用してきた。

今回のIntelの発表から、同社が幅広い技術ポートフォリオを開発中であることが分かる。いずれの技術も、業界の標準化を推進するまでには至らないようだが、Intel製品の高性能化を実現するとみられている。

新しい技術を採用することにより、パッケージングインターコネクトのサイズを、現在の50mmからさらに縮小できるようになる他、1mm2当たりのI/O密度を、現在の数百から、数万にまで高めることも可能になるとする。

幾つかの課題もあるようだ。IntelのフェローであるRavi Mahajan氏は、「ピッチ20〜35μmのどこかで、はんだベースのインターコネクトから、はんだを使わないインターコネクトへと移行する必要があるだろう」と述べている。

また、一部のチップスタックの歩留まりが約20%と低い点も、大きな課題となっている。Intelは、自社開発したチップテスター向けに、新型モジュールを開発した。個々のダイがモジュールでどのように機能するのかをうまく判断することにより、8層のチップスタックの歩留まりを70%以上に高めることが可能だという。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

半導体業界のトレンドは「3次元化」が明確に VLSI 2019

半導体業界のトレンドは「3次元化」が明確に VLSI 2019

2019年のVLSIシンポジウム(以下、VLSI)が6月9〜14日に、京都のリーガロイヤルホテルで開催された。今後の半導体業界の進む方向性を伺える内容が多かったのでレポートする。 Intelが7nm開発にメド、2021年に市場投入を予定

Intelが7nm開発にメド、2021年に市場投入を予定

Intelの経営幹部は、同社の投資家向けの年次ミーティングにおいて「当社の10nmプロセッサは、これまで出荷予定に遅れが生じていたが、今回は、2018年に発表したスケジュール通り、2019年6月に出荷を開始できる見込みだ」と述べた。7nmプロセッサの出荷を2021年に予定していることも明らかにした。 Samsungが5nmプロセスの開発を完了、2020年に量産

Samsungが5nmプロセスの開発を完了、2020年に量産

Samsung Electronics(以下、Samsung)は、EUV(極端紫外線)を用いた5nmプロセスの開発が完了し、受注を開始したと発表した。 エレクトロニクスと実装技術の将来を展望するロードマップ

エレクトロニクスと実装技術の将来を展望するロードマップ

今回から、JEITAが作成した「2019年度版 実装技術ロードマップ」の概要を紹介していく。まずは、2019年6月4日に開催された同書の完成報告会のプログラムと、ロードマップ本体の目次を見てみよう。【訂正あり】 ミニマルファブ、半導体チップの試作も活発に

ミニマルファブ、半導体チップの試作も活発に

ミニマルファブ推進機構は、「SEMICON Japan 2018」で、「ミニマルファブ、先端へ」をキャッチフレーズに、新開発のミニマルファブ向け製造装置や、ミニマルファブ装置で製作した実チップなどを展示した。 19年Q1の半導体売上高、Intelが首位に返り咲き

19年Q1の半導体売上高、Intelが首位に返り咲き

市場調査会社のIC Insightsによると、2019年第1四半期における半導体売上高ランキングにおいて、メモリ市場の低迷からSamsung Electronics(以下、Samsung)が2位に落ち、Intelが首位に返り咲いた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待