微細配線が可能なFO-WLPの組み立て技術:福田昭のデバイス通信(218) 2019年度版実装技術ロードマップ(29)(2/2 ページ)

支持ウエハーで平坦度を維持して微細な再配線層を形成可能に

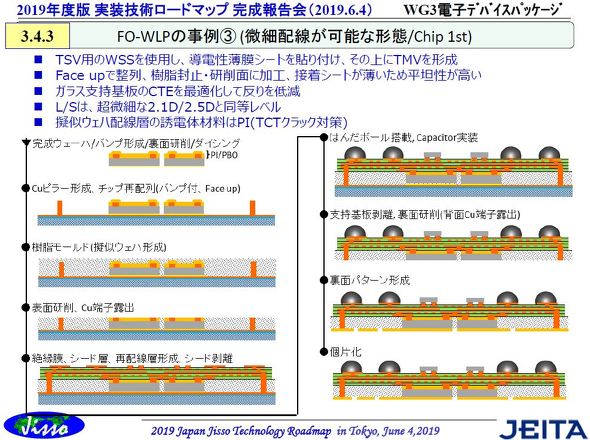

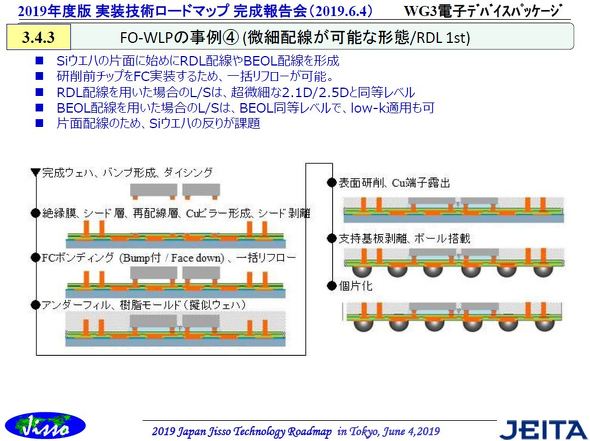

以下に10μm未満の微細配線が可能なFO-WLPの組み立て工程を示そう。大別すると2種類の構造(工程)がある。1つはシリコンダイを始めに搭載する「チップファースト(Chip First)」、もう1つは再配線層を始めに形成する「RDLファースト(RDL First)」である。

最初は「チップファースト(Chip First)」タイプの組み立てフローを説明しよう。まずガラスウエハー(支持ウエハー)に導電性シートを貼り、続いて銅(Cu)箔を貼る。銅箔をベースに、パッケージオンパッケージ(PoP:Package on Package)用のCuピラーを形成しておく。なおPoPではない場合は、Cu箔を貼る工程とCuピラーを形成する工程を省く。

シリコンダイは、完成ウエハーにCuバンプを搭載して裏面を研削し、各ダイに分割した状態にある。このダイをフェースアップ(回路面を上にした状態)で支持ウエハーに搭載する。それから全体をモールド樹脂で封止する。

その後モールド樹脂の表面(回路面)を研削してCuバンプとCuピラーを露出させる。それから再配線層(RDL)を形成する。このとき支持ウエハーによって表面の平坦度が維持されているので、再配線層の線幅/間隔を微細にできる。線幅/間隔は内層で2μm/2μmと極めて狭い。外層でも5μm/5μmと微細である。

次にはんだボールとチップキャパシター(チップコンデンサー)を表面に搭載する。続いて支持ウエハーを剥離し、裏面を研削してCuピラーを露出させる。それからCu配線を形成する。このCu配線はPoP用である。最後にパッケージを個別に分離する。

なおこの構造では、支持ウエハーのガラス材料の熱膨張係数を調整して反りを低減している。またRDLのシリコンダイ側の誘電体層にポリイミドとポリベンゾオキサゾールの2層構造を採用してシリコンダイ端部の応力を緩和し、温度サイクルによるクラックの発生を防いでいる。

シリコンダイを一括リフローで再配線層と接続

ここからは「RDLファースト(RDL First)」タイプの組み立てフローを説明しよう。シリコンあるいはガラスの平坦なウエハー(支持ウエハー)にまず、再配線層とCuピラー(PoPの場合)を形成する。再配線層の線幅/間隔は2μm/2μm〜10μm/10μmである。

シリコンダイは完成ウエハーにはんだバンプを搭載し、各ダイに分割した状態にある。裏面研削はしていない。このダイをフェースダウン(回路面を下にした状態)で支持ウエハーに搭載する。続いて一括リフローによってシリコンダイと再配線層を接続する。シリコンダイは裏面研削していないので厚みがあり、一括リフローでも反らない。

それからシリコンダイと再配線層の間に樹脂を注入して硬化させる(アンダーフィル)。そして全体をモールド樹脂で封止する。モールド樹脂の表面(シリコンダイの裏面側)を研削してCuピラーを露出させる。次に支持ウエハーを剥離し、はんだボールを裏面(底面)に搭載する。最後にパッケージを個別に分離する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

1個のパッケージでシステムを実現するSiP

1個のパッケージでシステムを実現するSiP

今回は、SiP(System in Package)を実現する幾つかの手法のうち、2.X次元(2.XD)の実装技術を解説する。ここでカギとなるのは、インタポーザだ。 小型・薄型・低コストのパッケージを実現する組み立て技術

小型・薄型・低コストのパッケージを実現する組み立て技術

今回から、パッケージの組み立てプロセスの技術動向を紹介する。まずは、QFN、BGA、WL-CSP、FO-WLPの組み立て工程を取り上げる。 多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

パッケージの組み立てプロセス技術を紹介している。今回は、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。 パッケージング技術開発の40億円プロジェクト、EUで始動

パッケージング技術開発の40億円プロジェクト、EUで始動

欧州は、オプティクスやフォトニクスなどの、複雑なシステムや最先端パッケージングに対する需要の高まりを受け、製造およびパッケージング関連の価値連鎖を維持しながら活性化させることができるのだろうか。EUの「Applause」プロジェクトは、フォトニクスやオプティクス、エレクトロニクス向けに低コスト製造を実現するための最先端パッケージング技術を提供するという、欧州の野心を示している。 メモリチップの生産性を向上するダイセパレーター

メモリチップの生産性を向上するダイセパレーター

ディスコは2019年12月2日、300mmウエハー対応のフルオートマチックダイセパレーター「DDS2320」を開発したと発表した。メモリ生産においてスループットと信頼性の向上を実現できると同社は述べる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- デンソー、ロームに対する株式取得提案を正式表明

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- ソニー・ホンダモビリティ、EV「AFEELA」開発中止

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響